## TX32M2300 数据手册

|      |            |                |       |                |

|------|------------|----------------|-------|----------------|

| 保密等级 | A          | TX32M2300 数据手册 | 文件 编号 | TX-TX8C1260-RD |

| 发行日期 | 2023-04-11 |                | 文件 版本 | V2.2           |

## 修订记录

| 日期         | 版本   | 描述                       |

|------------|------|--------------------------|

| 2023-04-11 | V2.2 | 1、修改比较器部分关于正端和负端输入的选择描述； |

| 2023-02-03 | V2.1 | 1、解决部分设备打开阅读时，出现乱码问题；    |

| 2022-08-12 | V2.0 | 1、重新整理了文档的格式；            |

### 注意：

- 本公司保留对以下所有产品在功能、性能、方案、设计及改进方面的最终解释权。

- 本公司保留对文档复制及更改的权利。

## 目录

|                                   |    |

|-----------------------------------|----|

| TX32M2300 数据手册 .....              | 1  |

| 1. 总介 .....                       | 1  |

| 1. 1. 概述 .....                    | 1  |

| 1. 2. 产品特性 .....                  | 1  |

| 2. 系统及存储器架构 .....                 | 4  |

| 2. 1. 32 位 RISC 处理器 .....         | 5  |

| 2. 2. 系统架构 .....                  | 5  |

| 2. 3. 存储器映射 .....                 | 7  |

| 2. 3. 1. 位带操作 .....               | 8  |

| 2. 3. 2. 片上 SRAM 存储器 .....        | 9  |

| 2. 3. 3. 片上 FLASH 存储器概述 .....     | 9  |

| 2. 3. 4. 引导配置 .....               | 10 |

| 2. 4. MCLR 功能 .....               | 10 |

| 3. 嵌入式闪存 .....                    | 10 |

| 3. 1. 闪存主要特性 .....                | 10 |

| 3. 2. 闪存功能描述 .....                | 10 |

| 3. 2. 1. 闪存结构 .....               | 10 |

| 3. 2. 2. 闪存读保护 .....              | 11 |

| 3. 2. 3. 闪存烧写和擦除操作 .....          | 12 |

| 3. 3. 寄存器 .....                   | 12 |

| 3. 3. 1. 寄存器基地址 .....             | 12 |

| 3. 3. 2. 寄存器列表 .....              | 12 |

| 3. 3. 3. 寄存器详细说明 .....            | 13 |

| 4. 中断和事件 .....                    | 19 |

| 4. 1. 嵌套向量中断控制器 .....             | 19 |

| 4. 2. 系统嘀嗒 (SysTick) 校准值寄存器 ..... | 19 |

| 4. 3. 中断功能描述 .....                | 19 |

| 4. 4. 外部中断/事件控制器 (EXTI) .....     | 21 |

| 4. 4. 1. 主要特征 .....               | 21 |

| 4. 4. 2. 唤醒事件管理 .....             | 22 |

| 5. CRC 计算单元 .....                 | 98 |

| 5. 1. 主要特性 .....                  | 98 |

| 5. 2. 寄存器 .....                   | 99 |

| 5. 2. 1. 寄存器基地址 .....             | 99 |

| 5. 2. 2. 寄存器列表 .....              | 99 |

|                                     |     |

|-------------------------------------|-----|

| 5.2.3. 寄存器详细说明.....                 | 99  |

| 5.3. 操作流程.....                      | 101 |

| 6. 电源控制 (power control) .....       | 22  |

| 6.1. 电源.....                        | 22  |

| 6.1.1. 电压调节器.....                   | 22  |

| 6.2. 电源管理器.....                     | 23  |

| 6.2.1. 上电复位 (POR) 和掉电复位 (PDR) ..... | 23  |

| 6.2.2. 可编程电压监测器 (PVD) .....         | 23  |

| 6.3. 低功耗模式.....                     | 24  |

| 6.4. 寄存器.....                       | 25  |

| 6.4.1. 寄存器基址.....                   | 25  |

| 6.4.2. 寄存器列表.....                   | 25  |

| 6.4.3. 寄存器详细说明.....                 | 25  |

| 7. 复位和时钟控制.....                     | 27  |

| 7.1. 复位.....                        | 27  |

| 7.1.1. 系统复位.....                    | 27  |

| 7.2. 主复位.....                       | 27  |

| 7.2.1. 电源复位.....                    | 27  |

| 7.3. 时钟.....                        | 28  |

| 7.3.1. XOSC 时钟.....                 | 28  |

| 7.3.2. HIRC 时钟.....                 | 28  |

| 7.3.3. PLL.....                     | 28  |

| 7.3.4. LIRC 时钟.....                 | 28  |

| 7.3.5. 系统时钟 (SYSCLK) 选择.....        | 29  |

| 7.3.6. DBSCLK 选择.....               | 29  |

| 7.3.7. LVDDBS_CLK 时钟选择.....         | 29  |

| 7.3.8. CMPCLK 时钟选择.....             | 30  |

| 7.3.9. 时钟安全系统 (CSS) .....           | 31  |

| 7.4. 寄存器.....                       | 31  |

| 7.4.1. 寄存器基址.....                   | 31  |

| 7.4.2. 寄存器列表.....                   | 31  |

| 7.4.3. 寄存器定义.....                   | 32  |

| 8. GPIO.....                        | 50  |

| 8.1. GPIO 主要特征.....                 | 50  |

| 8.2. GPIO 功能描述.....                 | 50  |

| 8.2.1. 通用 IO (GPIO) .....           | 51  |

| 8.2.2. 单独的位操作.....                  | 52  |

| 8.2.3. 复用功能 (AF) .....              | 52  |

| 8.2.4. GPIO 锁定机制.....               | 52  |

|                        |     |

|------------------------|-----|

| 8.2.5. 输入配置.....       | 52  |

| 8.2.6. 输出配置.....       | 53  |

| 8.2.7. 模拟输入配置.....     | 53  |

| 8.3. 寄存器.....          | 54  |

| 8.3.1. 寄存器基地址.....     | 54  |

| 8.3.2. 寄存器列表.....      | 54  |

| 8.3.3. 寄存器详细定义.....    | 55  |

| 9. 通信接口外设 CSI.....     | 72  |

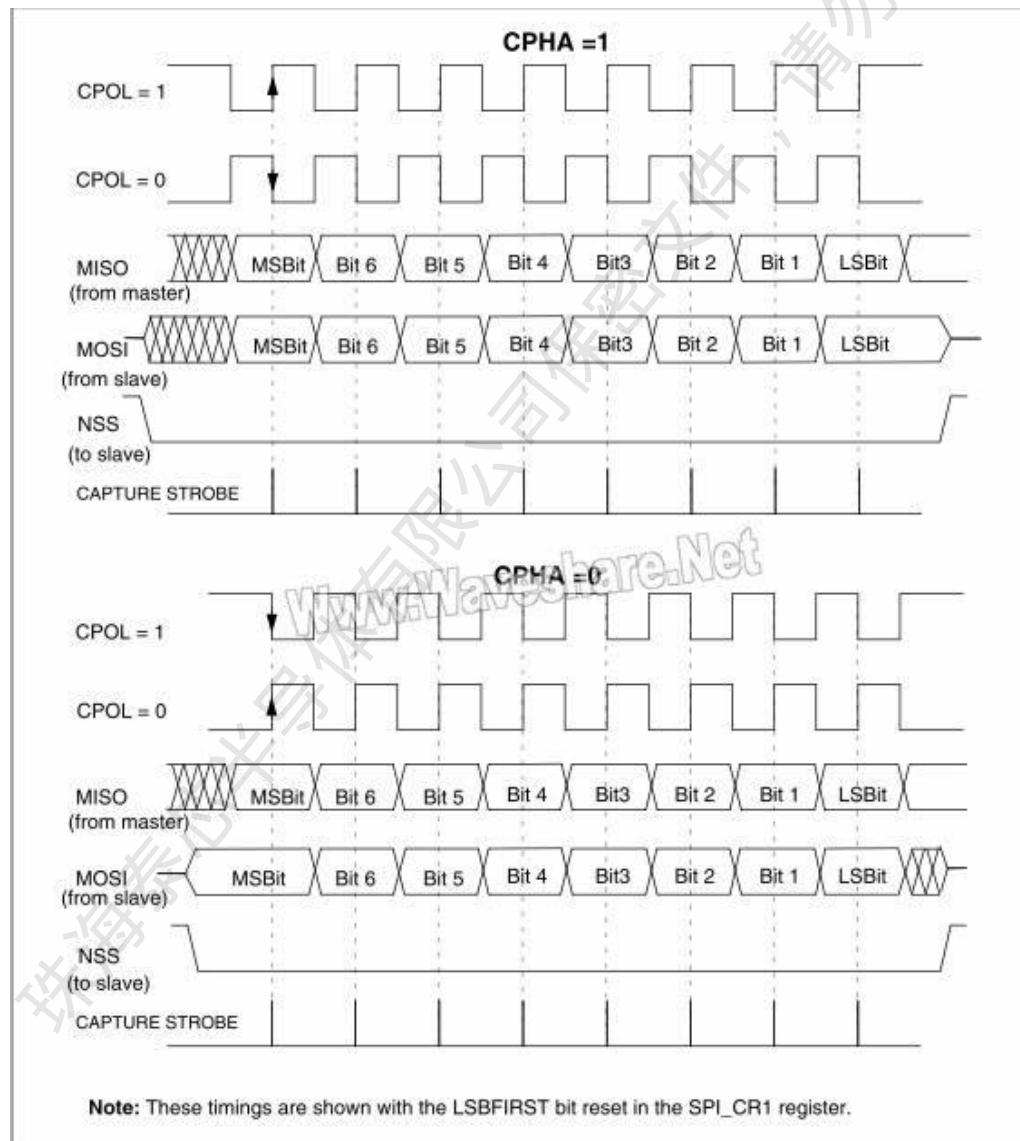

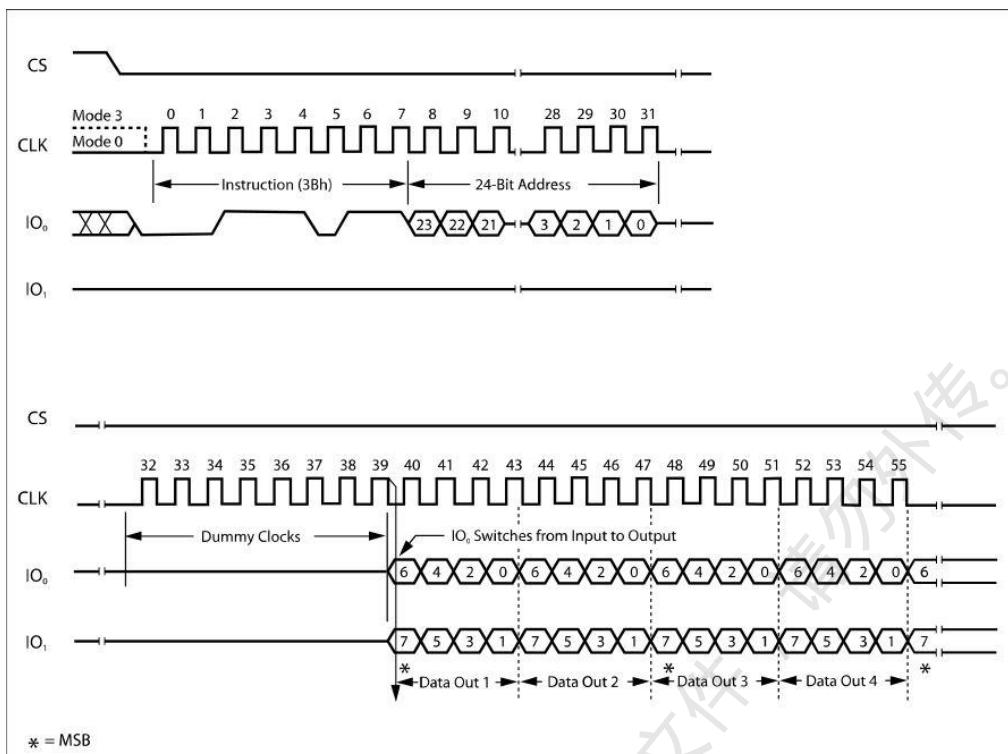

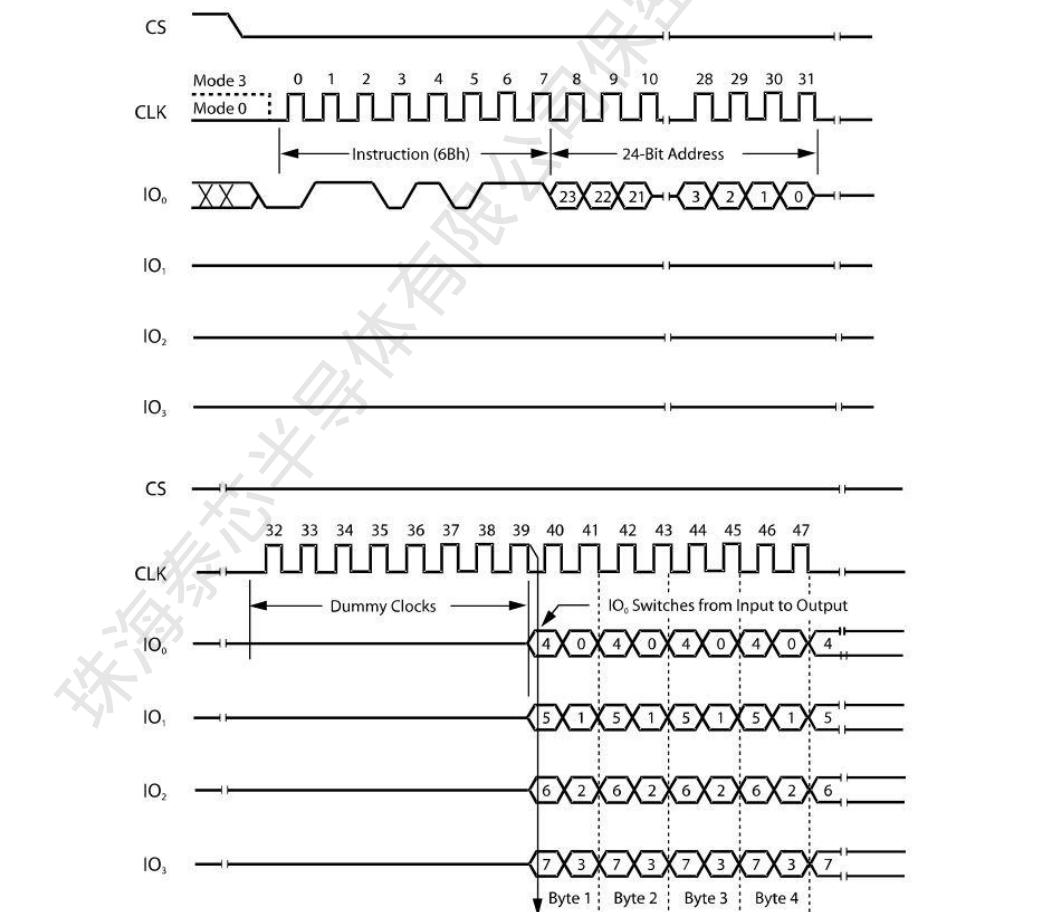

| 9.1. SPI_I2C.....      | 72  |

| 9.1.1. SPI 功能描述.....   | 72  |

| 9.1.2. I2C 功能描述.....   | 73  |

| 9.1.3. SPI 时序图.....    | 73  |

| 9.1.4. IO MAPPING..... | 75  |

| 9.2. 寄存器.....          | 75  |

| 9.2.1. 寄存器基地址.....     | 75  |

| 9.2.2. 寄存器列表.....      | 75  |

| 9.2.3. 寄存器详细说明.....    | 76  |

| 9.2.4. 使用说明.....       | 82  |

| 10. UART.....          | 87  |

| 10.1. 概述.....          | 87  |

| 10.2. 寄存器.....         | 88  |

| 10.2.1. 寄存器基地址.....    | 88  |

| 10.2.2. 寄存器列表.....     | 88  |

| 10.2.3. 寄存器详细说明.....   | 89  |

| 10.2.4. 使用说明.....      | 96  |

| 11. 硬件加速单元.....        | 102 |

| 11.1. 加速单元简介.....      | 102 |

| 11.2. 硬件除法主要特征.....    | 102 |

| 11.3. 硬件除法功能介绍.....    | 102 |

| 11.4. 寄存器.....         | 102 |

| 11.4.1. 寄存器基地址.....    | 102 |

| 11.4.2. 寄存器列表.....     | 103 |

| 11.4.3. 寄存器详细说明.....   | 103 |

| 12. 比较器 (COMP) .....   | 104 |

| 12.1. 简介.....          | 104 |

| 12.2. 主要特性.....        | 104 |

| 12.3. 功能描述.....        | 105 |

| 12.3.1. 比较器功能框图.....   | 105 |

|                          |     |

|--------------------------|-----|

| 12.3.2. 比较器输入和输出.....    | 106 |

| 12.3.3. 比较器工作模式.....     | 106 |

| 12.3.4. 比较器滤波控制.....     | 107 |

| 12.3.5. 比较器轮询周期.....     | 107 |

| 12.3.6. 比较器中断和唤醒.....    | 108 |

| 12.3.7. 比较器锁定机制.....     | 108 |

| 12.3.8. 比较器迟滞现象.....     | 108 |

| 12.4. 寄存器.....           | 108 |

| 12.4.1. 寄存器基址.....       | 108 |

| 12.4.2. 寄存器列表.....       | 109 |

| 12.4.3. 寄存器详细说明.....     | 109 |

| 13. 运算放大器 (OPA) .....    | 113 |

| 13.1. 简介.....            | 113 |

| 13.2. 主要特征.....          | 113 |

| 13.3. 寄存器描.....          | 113 |

| 13.3.1. 寄存器基址.....       | 113 |

| 13.3.2. 寄存器列表.....       | 113 |

| 13.3.3. 寄存器详细说明.....     | 114 |

| 14. ADC.....             | 116 |

| 14.1. 功能简介.....          | 116 |

| 14.2. 主要特征.....          | 116 |

| 14.3. 结构框图.....          | 117 |

| 14.4. 功能描述.....          | 118 |

| 14.4.1. ADC 开关控制.....    | 118 |

| 14.4.2. 通道选择.....        | 118 |

| 14.4.3. ADC 工作模式.....    | 118 |

| 14.4.4. DMA 请求.....      | 119 |

| 14.4.5. 采样频率设置.....      | 119 |

| 14.4.6. 连续采样间隔时间可配置..... | 119 |

| 14.4.7. 外部触发转换.....      | 120 |

| 14.5. ADC 接口时序.....      | 120 |

| 14.5.1. ADC 上电时序.....    | 120 |

| 14.6. 寄存器.....           | 121 |

| 14.6.1. 寄存器基址.....       | 121 |

| 14.6.2. 寄存器列表.....       | 121 |

| 14.6.3. 寄存器详细说明.....     | 122 |

| -.....                   | 123 |

| 15. Timer.....           | 131 |

| 15.1. 简介.....            | 131 |

|                                                      |     |

|------------------------------------------------------|-----|

| 15.2. 主要特性.....                                      | 131 |

| 15.3. 功能描述.....                                      | 132 |

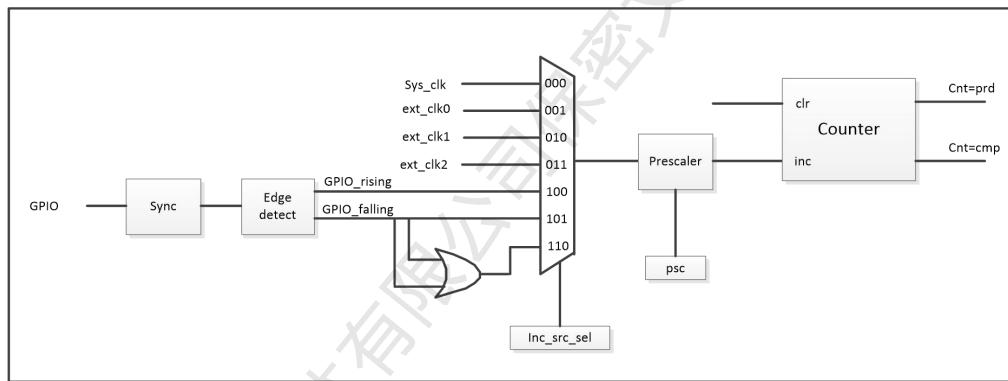

| 15.3.1. 时基单元.....                                    | 132 |

| 15.3.2. 计数源选择.....                                   | 133 |

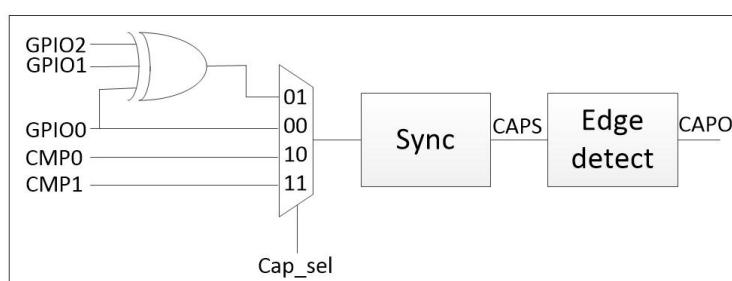

| 15.3.3. 输入捕获源.....                                   | 133 |

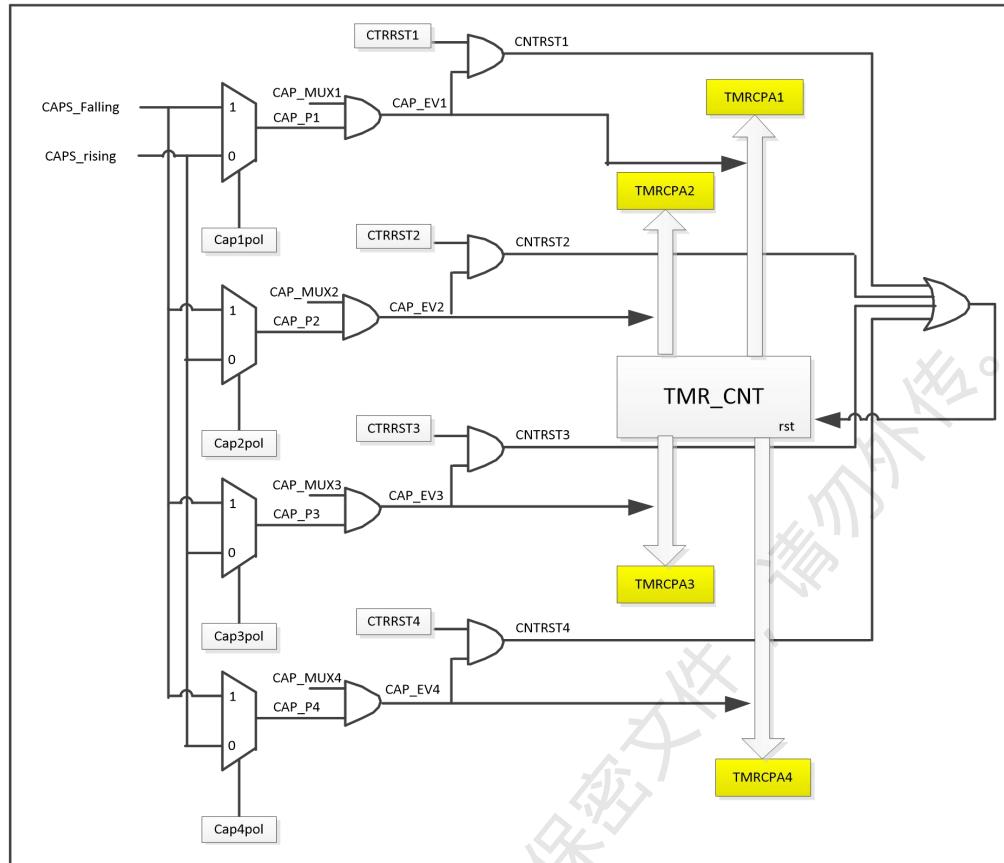

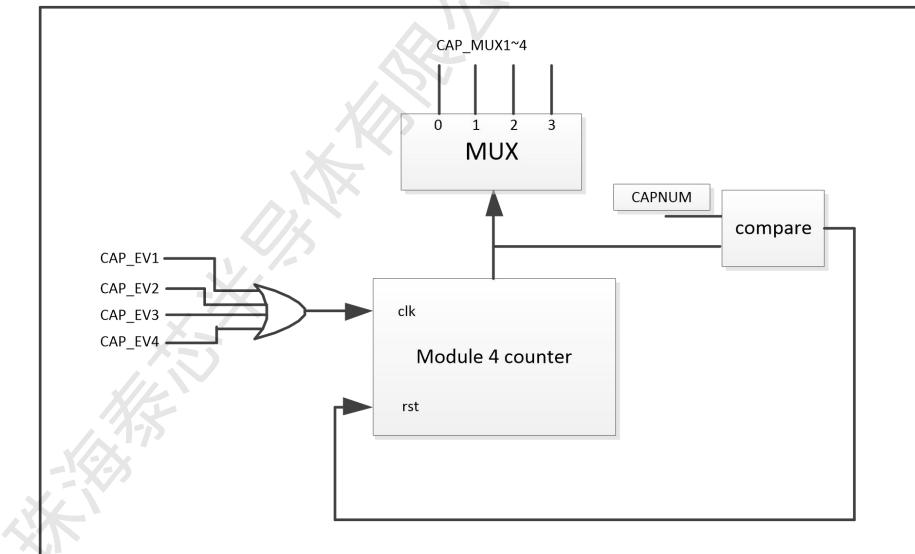

| 15.3.4. 输入捕获模式.....                                  | 134 |

| 15.3.5. PWM 模式.....                                  | 135 |

| 15.3.6. 触发 ADC 采样.....                               | 136 |

| 15.3.7. timer 同步输出.....                              | 136 |

| 15.3.8. 从模式.....                                     | 137 |

| 15.3.9. 复位模式.....                                    | 137 |

| 15.3.10. 触发模式.....                                   | 137 |

| 15.3.11. 门控模式.....                                   | 138 |

| 15.3.12. DMA 传输模式.....                               | 138 |

| 15.3.13. 多个 timer 之间级联.....                          | 139 |

| 15.3.14. 多个 timer 计数值同时清零.....                       | 139 |

| 15.3.15. 产生带载波的 PWM 信号.....                          | 140 |

| 15.4. 寄存器.....                                       | 140 |

| 15.4.1. 寄存器基地址.....                                  | 140 |

| 15.4.2. 寄存器列表.....                                   | 141 |

| 15.4.3. 寄存器详细说明.....                                 | 141 |

| 16. EPWM.....                                        | 146 |

| 16.1. 简介.....                                        | 146 |

| 16.2. 子模块介绍.....                                     | 147 |

| 16.2.1. 时基计数器子模块 (Time-base) .....                   | 147 |

| 16.2.2. 时基计数比较器子模块 (Counter-comparator) .....        | 148 |

| 16.2.3. 动作产生子模块 (Action-qualifier) .....             | 148 |

| 16.2.4. 死区产生子模块 (Dead-band) .....                    | 149 |

| 16.2.5. 事件触发子模块 (Event-trigger) .....                | 149 |

| 16.2.6. 故障区子模块 (Trip-zone) .....                     | 150 |

| 16.3. 功能描述及常用拓扑.....                                 | 150 |

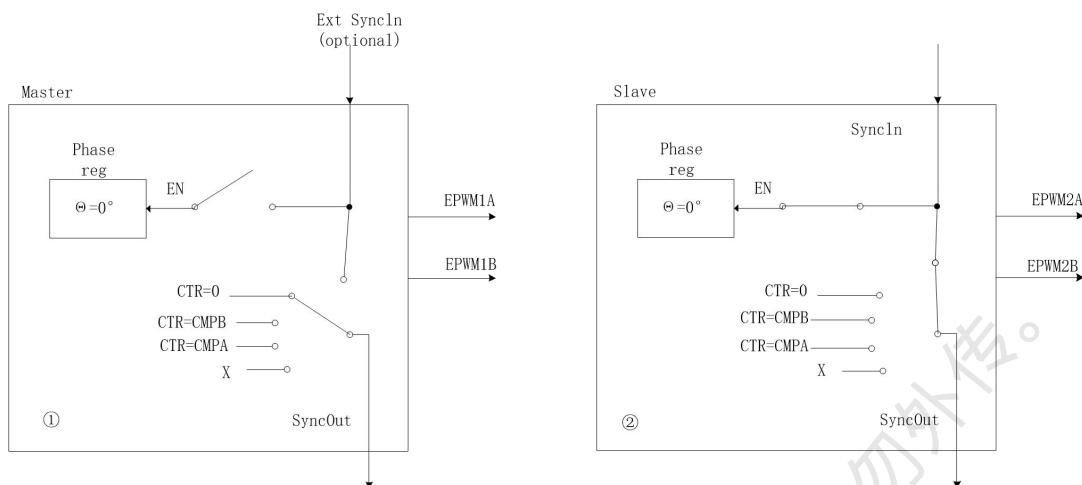

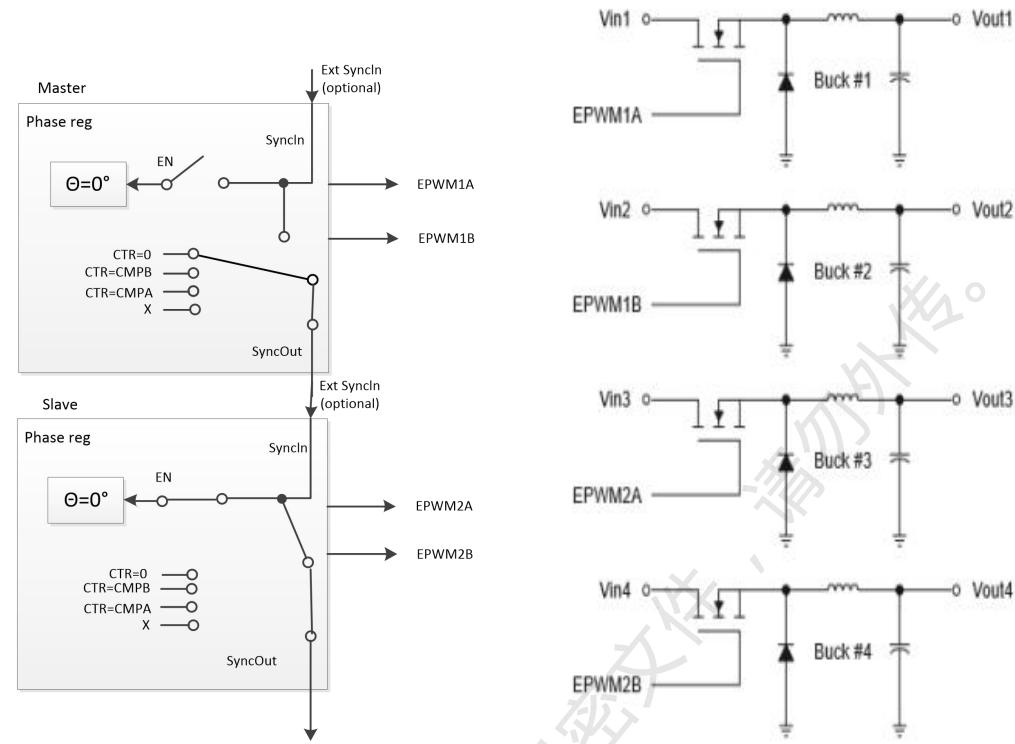

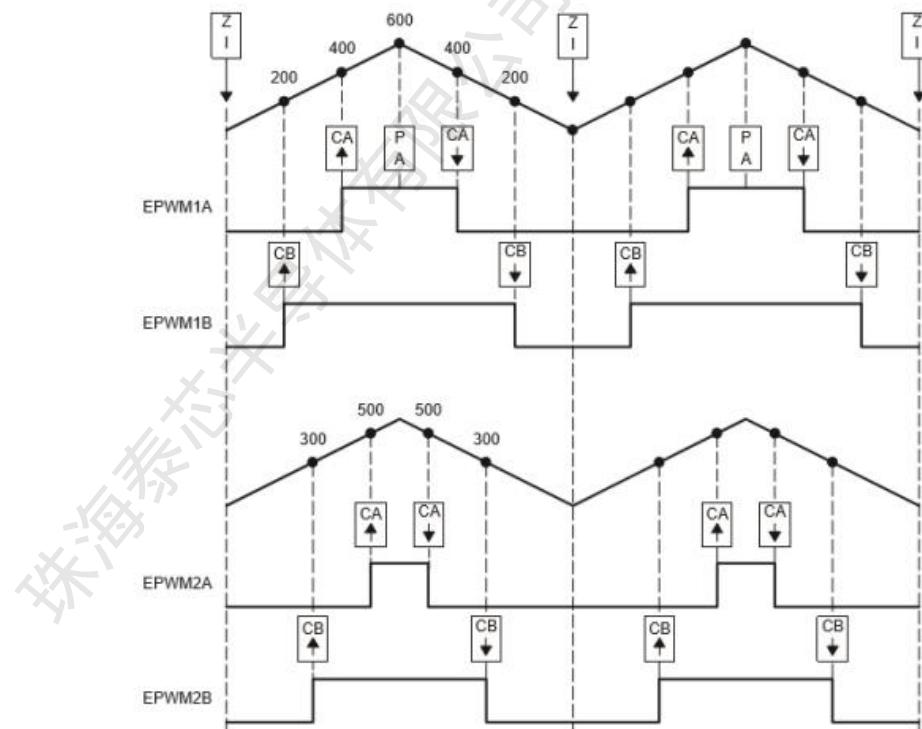

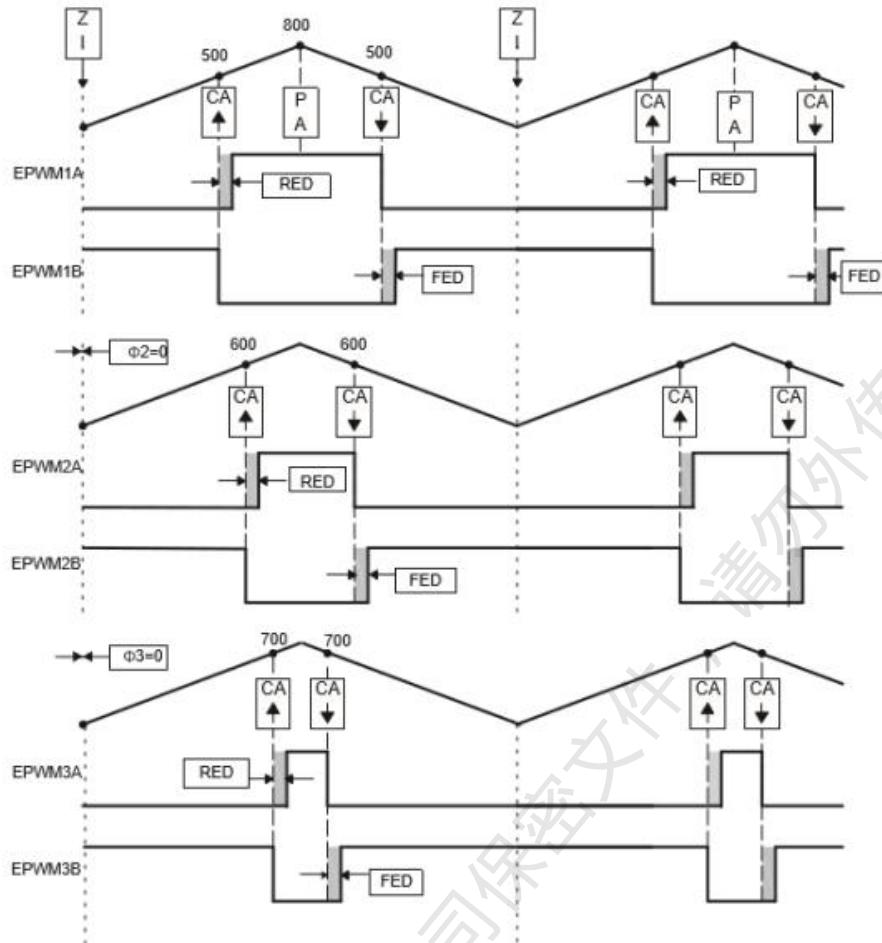

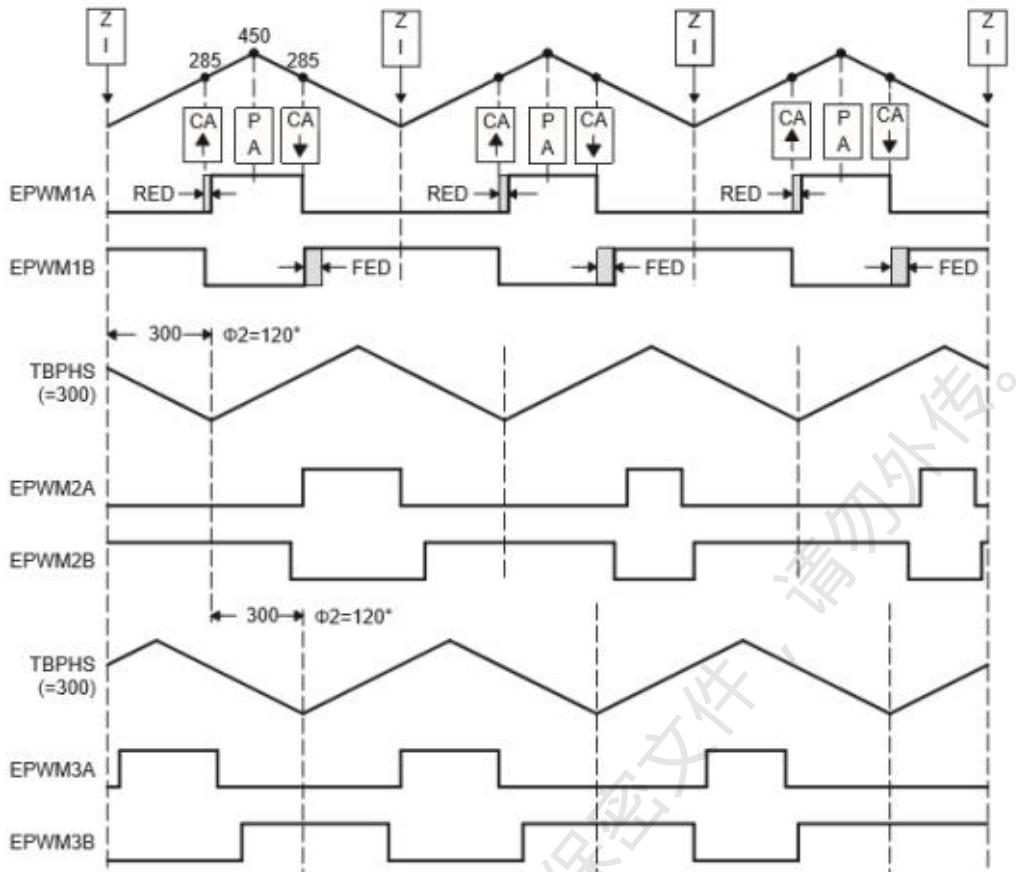

| 16.3.1. 独立频率控制多个 Buck 转换电路.....                      | 151 |

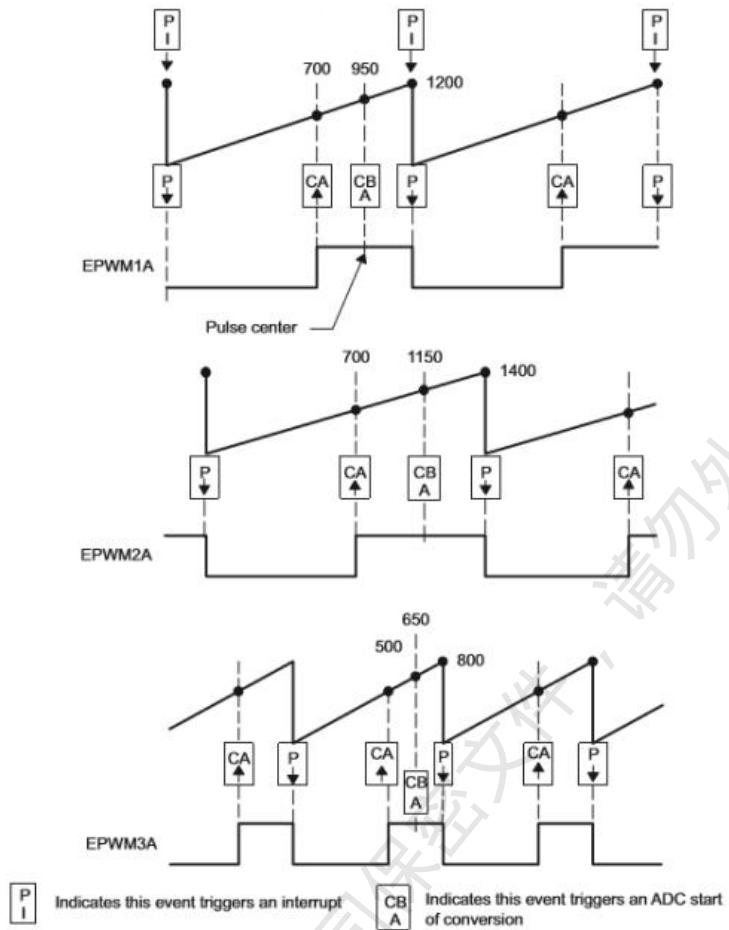

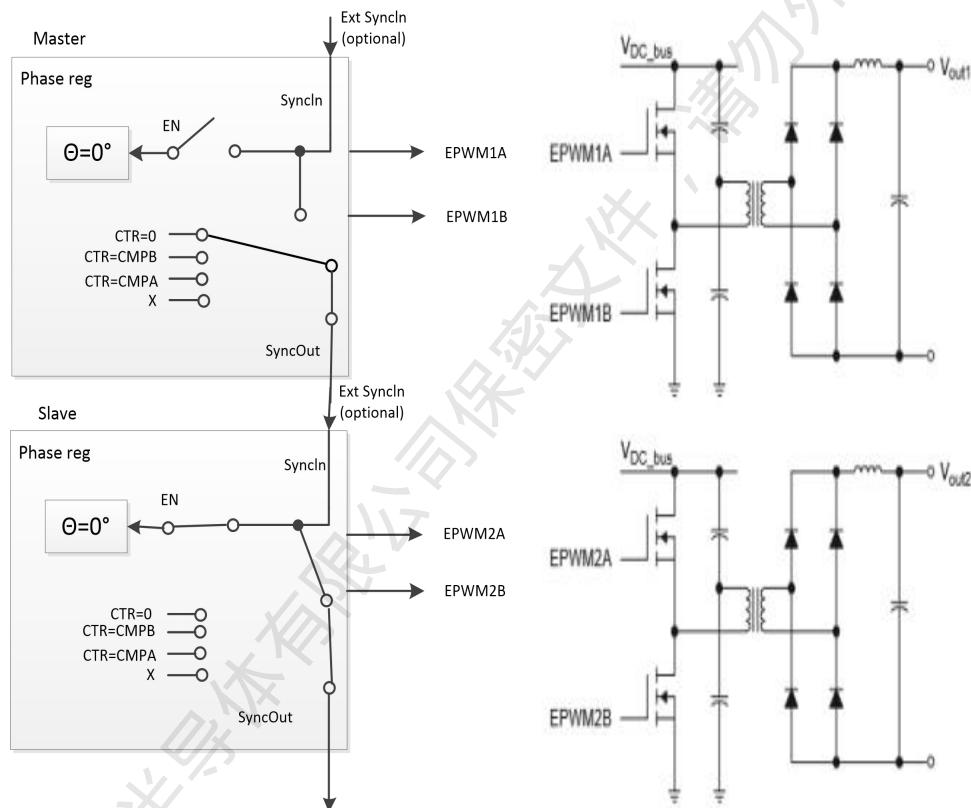

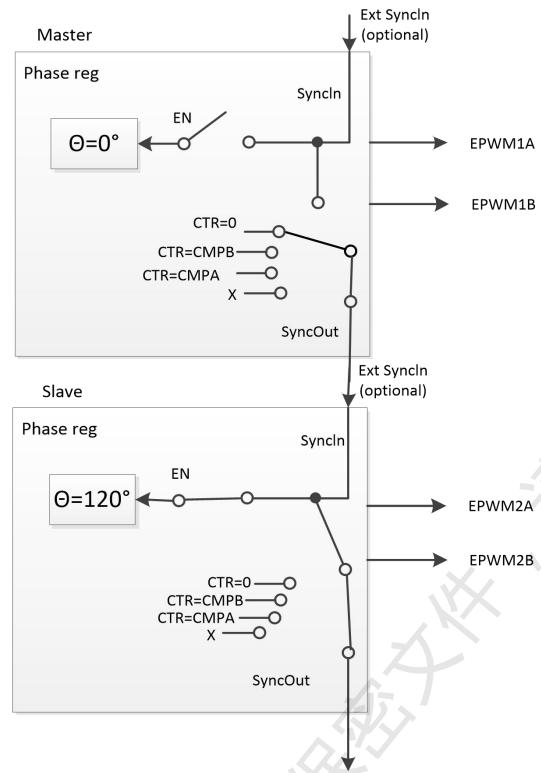

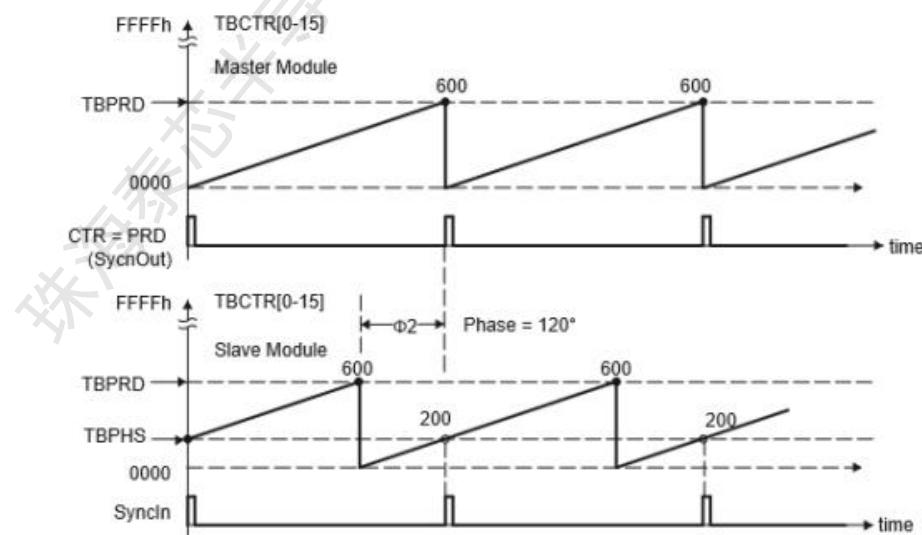

| 16.3.2. 相同频率控制多个 Buck 转换电路.....                      | 153 |

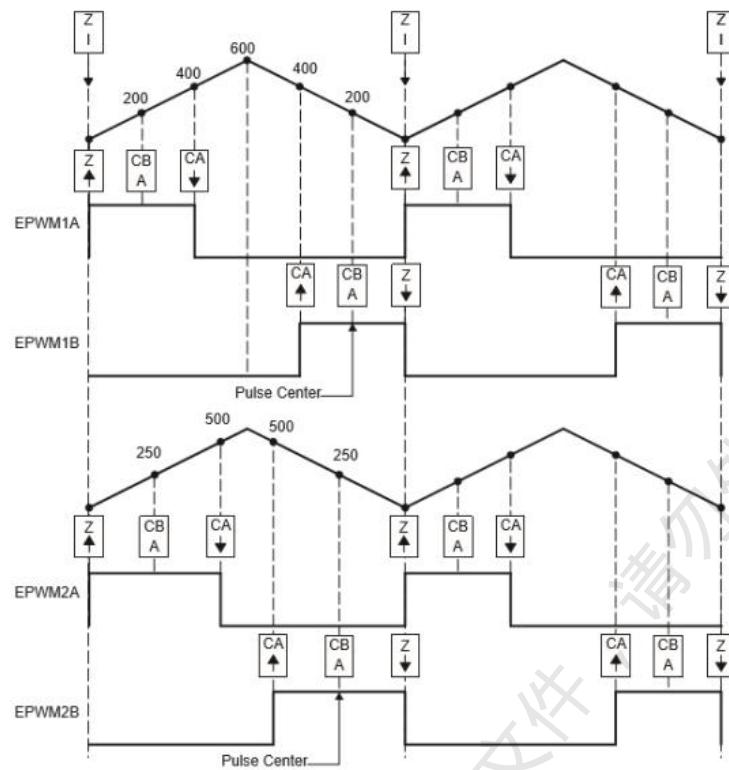

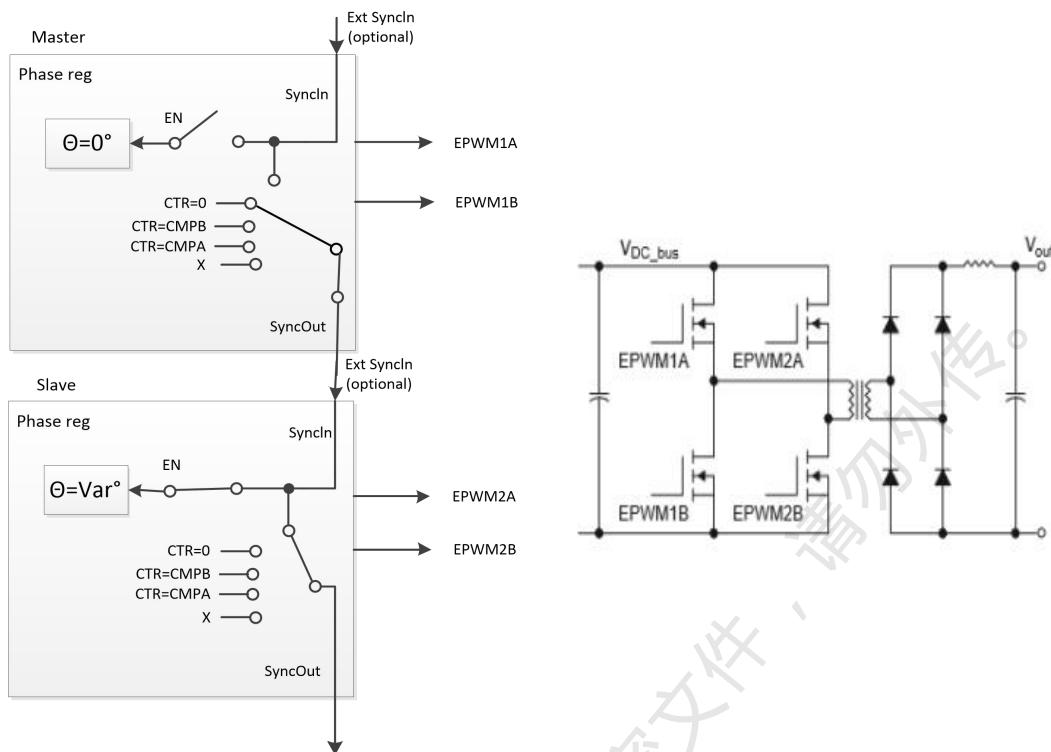

| 16.3.3. 控制多个 H 半桥电路 (HHB) 转换电路.....                  | 155 |

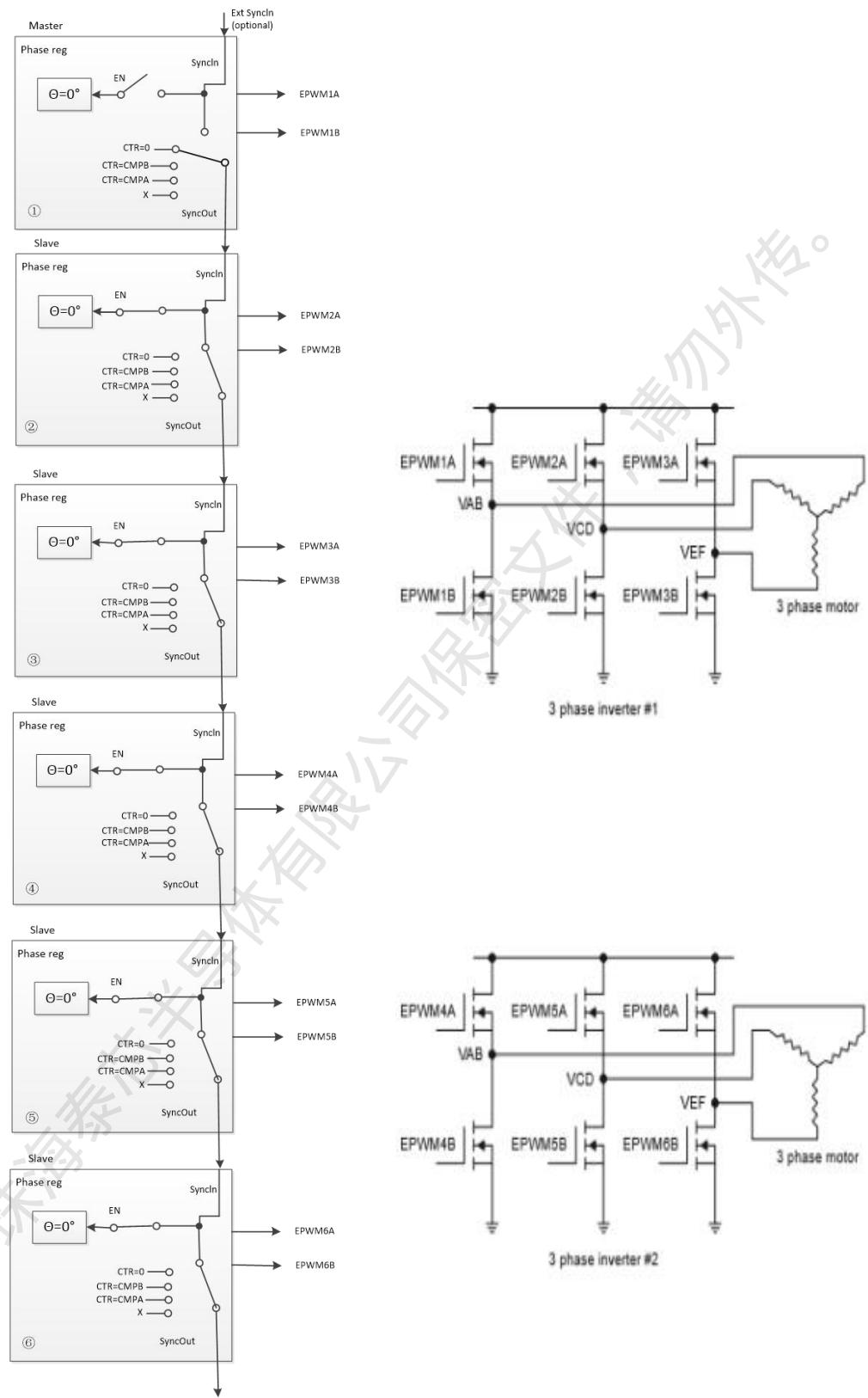

| 16.3.4. 控制电机的双三相逆变器 (ACI 和 PMSM) .....               | 156 |

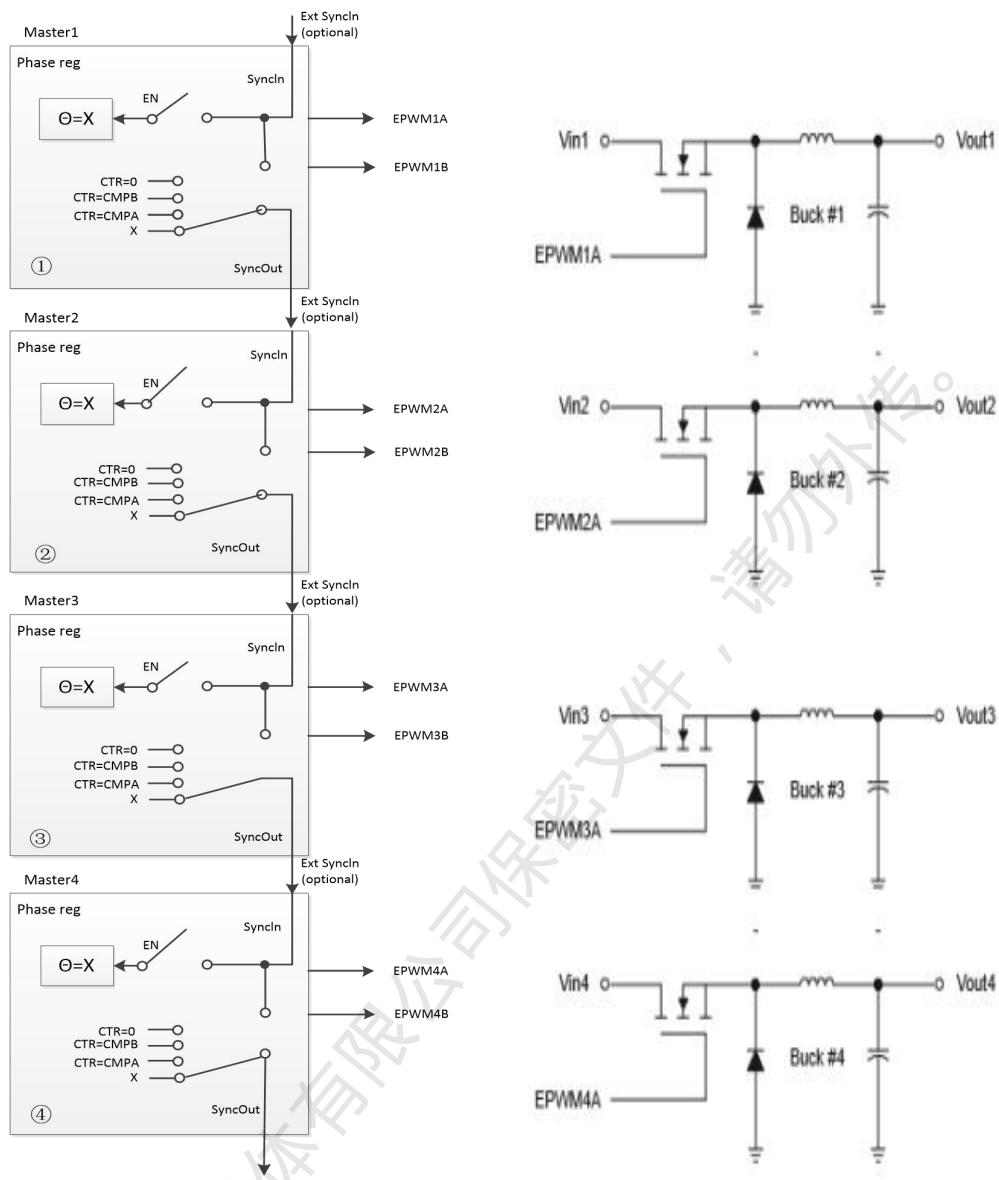

| 16.3.5. PWM 模块间相位控制的实际应用.....                        | 158 |

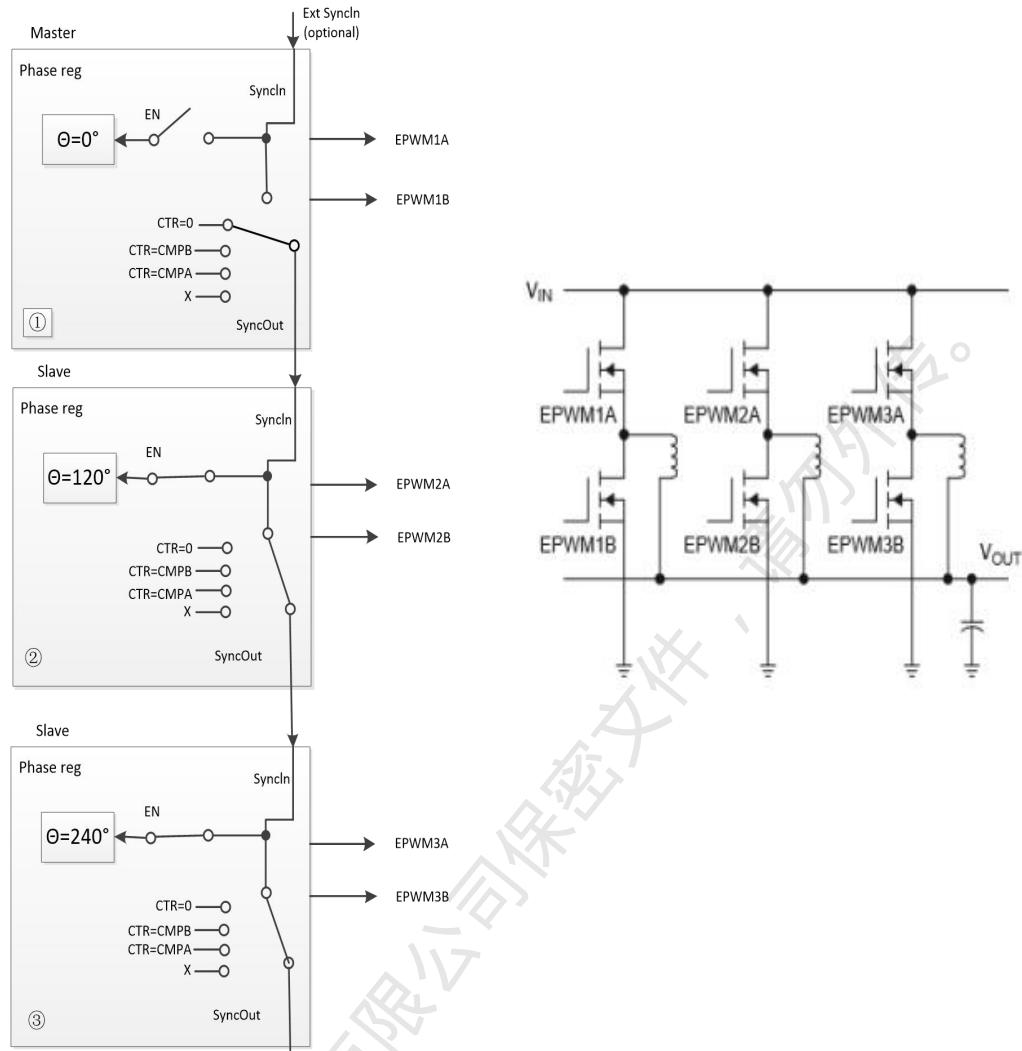

| 16.3.6. 控制三相交错 DC/DC 交换电路.....                       | 160 |

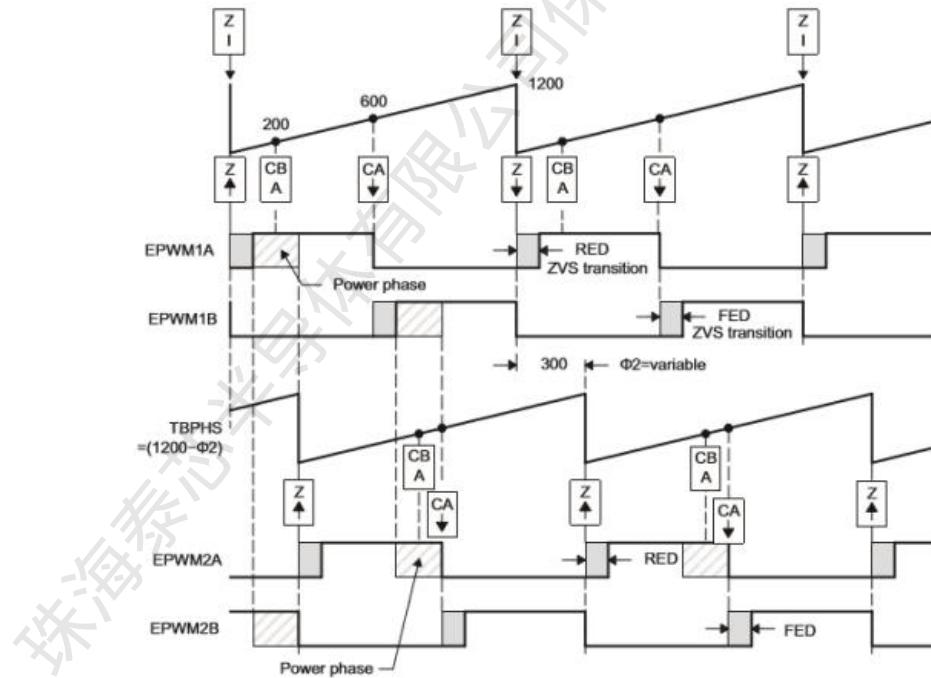

| 16.3.7. 控制 0 电压转换的全桥转换电路 (ZVSFB) .....               | 162 |

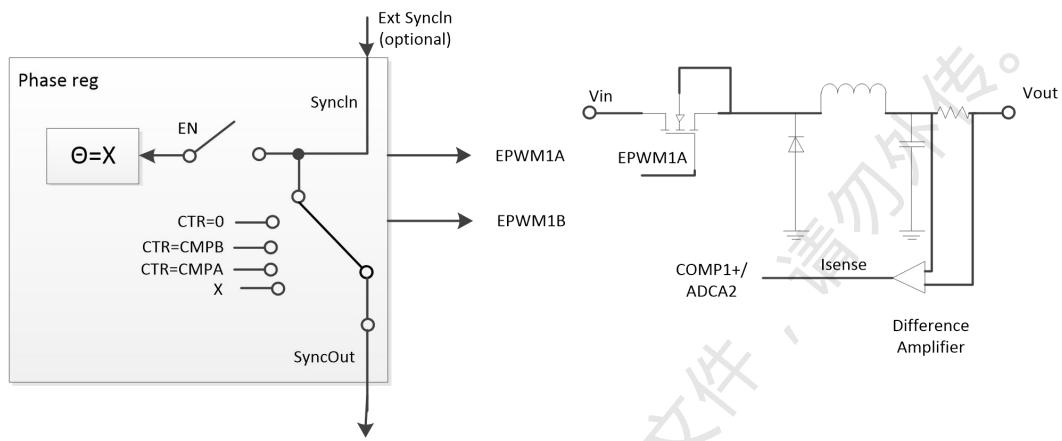

| 16.3.8. 控制峰值电流模式 (Peak Current Mode) 控制 Buck 模块..... | 163 |

| 16.3.9. 控制 H 桥 LLC 谐振变换器.....                        | 164 |

| 16.4. 寄存器.....                                       | 165 |

|                      |     |

|----------------------|-----|

| 16.4.1. 寄存器基地址.....  | 165 |

| 16.4.2. 寄存器列表.....   | 166 |

| 16.4.3. 寄存器详细说明..... | 167 |

| 17. WDT.....         | 188 |

| 17.1. 简介.....        | 188 |

| 17.2. 寄存器.....       | 189 |

| 17.2.1. 寄存器基地址.....  | 189 |

| 17.2.2. 寄存器列表.....   | 189 |

| 17.2.3. 寄存器详细说明..... | 189 |

# 1. 总介

## 1.1. 概述

本产品使用高性能的 32 位微控制器，最高工作频率可达 72MHz，内置 32KB 高速 Flash 存储器，6KB SRAM，丰富的增强型 I/O 端口和外设连接到外部总线。本产品包含 1 个 12 位的 ADC、一个 8 位精度 DAC、一个多功能比较器、3 个运算放大器、1 个 16 位高级定时器、5 个 16 位通用定时器、1 个 32 位通用定时器、1 个看门狗定时器、1 个系统滴答定时器。还包含标准的通信接口：2 个 SPI/IIC 接口和 2 个 UART 接口，其中 UART0 可以实现从任意一条 pin 里面选择一条进行代码升级，内置一个 32 位除 16 位有无符号除法器。

本产品产品系列工作电压为 2.0V~5.5V，工作温度范围-40°C ~ 105°C。多种省电工作模式保证低功耗应用的要求。

本产品提供 4 种封装，包括 LQFP32、SSOP28、SSOP24 和 TSSOP20。根据不同的封装形式，器件中的外设配置不尽相同。

下面给出了该系列产品中所有外设的基本介绍。

这些丰富的外设配置，使得本产品微控制器适合于多种应用场合：

- 风机，风扇等

- 消费类电子

- 智能家居

- 电机驱动和应用控制

- 医疗和手持设备

- 工业控制

- 工业应用：可编程控制器（PLC）、变频器、打印机和扫描仪

## 1.2. 产品特性

### ➤ 内核与系统

- 32-Bit RISC 架构的CPU

- 工作最大主频: 72MHz

- 单周期 32 位乘法指令

- 32 个中断源, 可配置 4 层中断优先级, 支持中断入口地址Remap

- 支持位带操作

- 支持双pin调试接口

## ➤ 存储器

- 32K Byte的闪存程序存储器(NO EEPROM Flash), Sector擦写次数 20000 次

- 内部 6K Byte SRAM

- Boot Loader 支持片内 Flash、支持单/双pin UART 在线用户编程 (IAP) / 在线系统编程 (ISP)

## ➤ 时钟、复位和电源管理

- 2V ~ 5.5V 供电

- 上电/断电复位 (POR/PDR)、可编程电压监测器 (PWD)

- 外部 1-32MHz晶体振荡器

- 内嵌经出厂调校的 26MHz (+/- 1.5%) 高速振荡器

- 内嵌 128KHz低速振荡器

- PLL输出 72MHz时钟

- 内置时钟安全系统 (CSS)

- WDT复位

## ➤ DMA 支持

- 支持的外设: EFLASH、UART、SPI/I2C、CRC、TIMER、ADC

## ➤ GPIO

- 最多能支持 30 个GPIO

- 所有 I/O 口可以触发边沿或电平响应中断, 唤醒低功耗模式

- 所有端口均可输入输出 5V 信号

- 支持按键检测

## ➤ 通讯接口外设

- 2 个 SPI 高速串行接口，Master 下最高支持系统时钟频率一半传输，支持 1/2/4 线主从模式，支持 I2C 模式

- 2 个 UART 接口，支持 RS232/RS485 协议，UART0 能支持任意 IO 程序升级

## ➤ 定时器

- 1 个 16 位高级定时器，支持 4 对互补输出或 8 个独立 PWM 输出，支持死区插入和事件刹车功能，支持单脉冲模式

- 5 个 16 位通用定时器，1 个 32 位定时器，每个定时器支持捕获功能

- 1 个看门狗定时器

- 1 个系统滴答定时器

## ➤ 硬件加速单元

- 硬件有符号除法器（32bit/16bit）

## ➤ 高安全性

- 支持 5/7/8/16/32 bit CRC 效验，保证数据准确性

- 支持代码加扰以及硬件加解密

## ➤ 低功耗

- 支持 IDLE、STOP、SLEEP 低功耗模式

- 静态功耗 < 20uA@25°C

- 低功耗唤醒时间最快 10us

## ➤ 1 个 12 位高速模数转换器

- 支持最高 1.2Mhz 采样率

- 多达 10 输入通道

## ➤ 1 个比较器

- 支持 7 个正端输入，3 个负端输入

- 支持硬件通道轮询

## ➤ 3 个运算放大器

- 同向放大器

- 内置 4/6/8/10/12 倍增益可配

- 闭环增益带宽可选

- **内置温度传感器**

- **高可靠性**

- ESD HBM 8KV

- EFT ±4500V

- Latch-up ±100mA @105°C

- **96 位的芯片唯一 ID (UID)**

- **封装**

- Die Form

- LQFP32/SSOP28/SSOP24/TSSOP20

- **工业级温度范围**

- -40°C ~ 105°C

- **应用**

- 风机等

- 电机驱动和应用控制

- 医疗和手持设备

- PC 游戏外设和 GPS 平台

- 工业应用：可编程控制器（PLC）、变频器、打印机和扫描仪

- 警报系统、视频对讲、和暖气通风空调系统等

## 2. 系统及存储器架构

TX32M2300 系列器件是基于 RISC 处理器的 32 位通用微控制器存储器的组织采用了哈佛结构，预先定义的存储器映射和高达 4 GB 的存储空间，充分保证了系统的灵活性和可扩展性。

## 2.1. 32 位 RISC 处理器

TX32M2300 系列所用的 32 位 RISC 处理器是一个具有低中断延迟时间和低成本调试特性的 32 位处理器。高集成度和增强的特性使这颗 RISC 处理器适合于那些需要高性能和低功耗微控制器的市场领域。

## 2.2. 系统架构

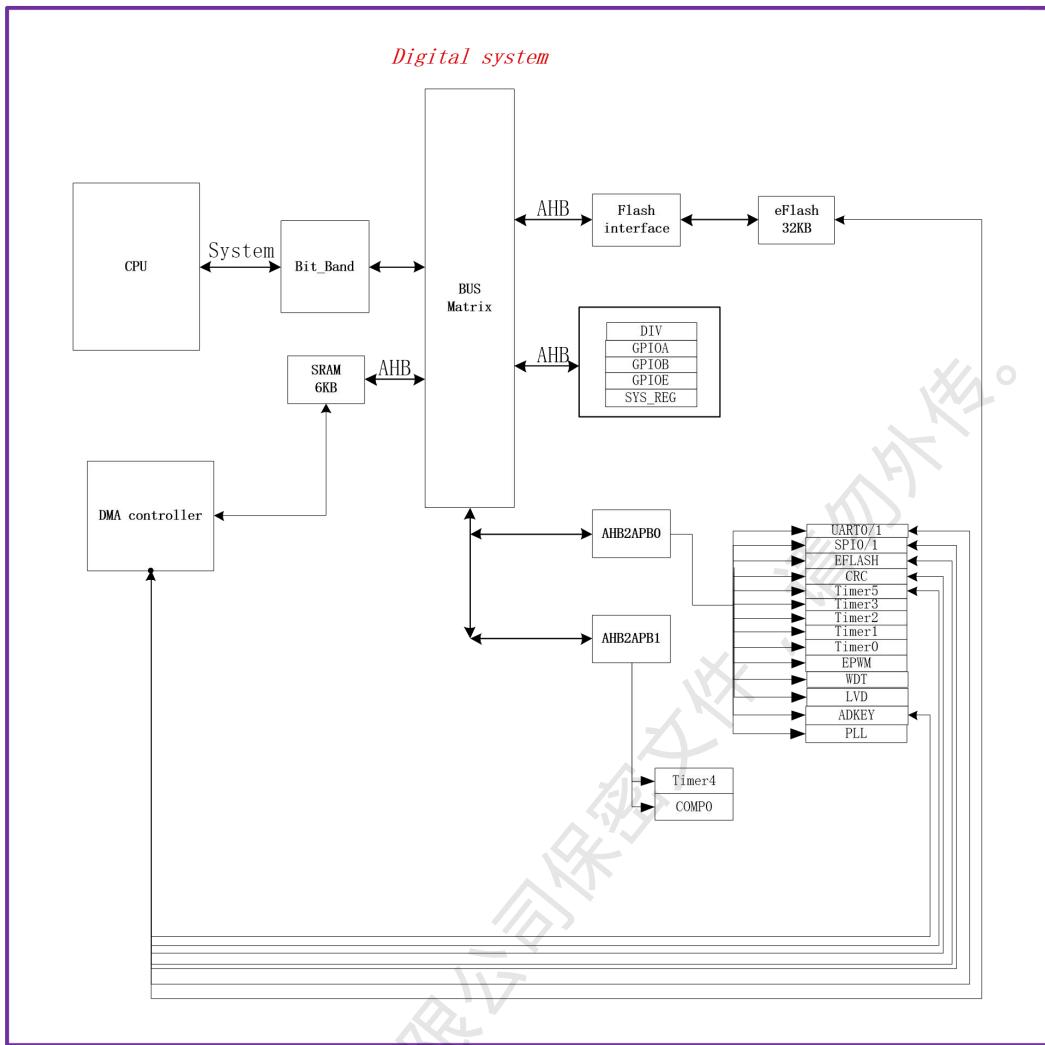

TX32M2300 系列器件采用 32 位多层总线结构，该结构可使系统中的多个主机和从机之间的并行通信成为可能。多层次总线结构包括一个 AHB 互联矩阵、两个 AHB 总线和两个 APB 总线。AHB 互联矩阵的互联关系接下来将进行说明。在系统主从互联矩阵的互联关系列表中，“1”表示相应的主机可以通过 AHB 互联矩阵访问对应的从机，空白的单元格表示相应的主机不可以通过 AHB 互联矩阵访问对应的从机。

TX32M2300 系列主系统由以下部分构成：

- 二个驱动单元：

- CPU 内核系统总线 (S-bus)

- DMA controller

- 三个被动单元

- 内部闪存存储器

- 内部 SRAM

- AHB 到 APB 的桥 (AHB2APB0/1)，它连接所有的 APB 设备

图 2-1 TX32M2300 系列总线系统架构图

### 系统总线

此总线连接 CPU 内核的系统总线（外设总线）到总线矩阵，总线矩阵协调着内核和各个高速部件间的访问。

#### DMA controller

此总线将 CPU 与各外设模块访问相联竞争，协调访问优先级，仲裁等。

表 2-1 DMA 模块使用的优先级排布

| 模块    | 优先级 | 说明 |

|-------|-----|----|

| CPU   | 0   | 最高 |

| SPI0  | 1   |    |

| SPI1  | 2   |    |

| UART0 | 3   |    |

| ADC   | 4   |    |

| UART1 | 5   |    |

| CRC   | 6   |    |

|        |   |    |

|--------|---|----|

| TIMER5 | 7 |    |

| Eflash | 8 | 最低 |

### 总线矩阵 (BusMatrix)

总线矩阵管理着内核系统总线与各外设模块的访问仲裁，总线矩阵由主模块总线及从模块总线组成。AHB 外设通过总线矩阵与系统总线相连。

#### AHB 到 APB 桥 (AHB2APB bridges-APB)

AHB 到 APB 桥在 AHB 与 APB 总线间提供同步连接。

注：当对 APB 寄存器进行 8 位或者 16 位访问时，该访问会被自动转换成 32 位的访问：桥会自动将 16 位或者 8 位的数据扩展以配合 32 位的宽度。

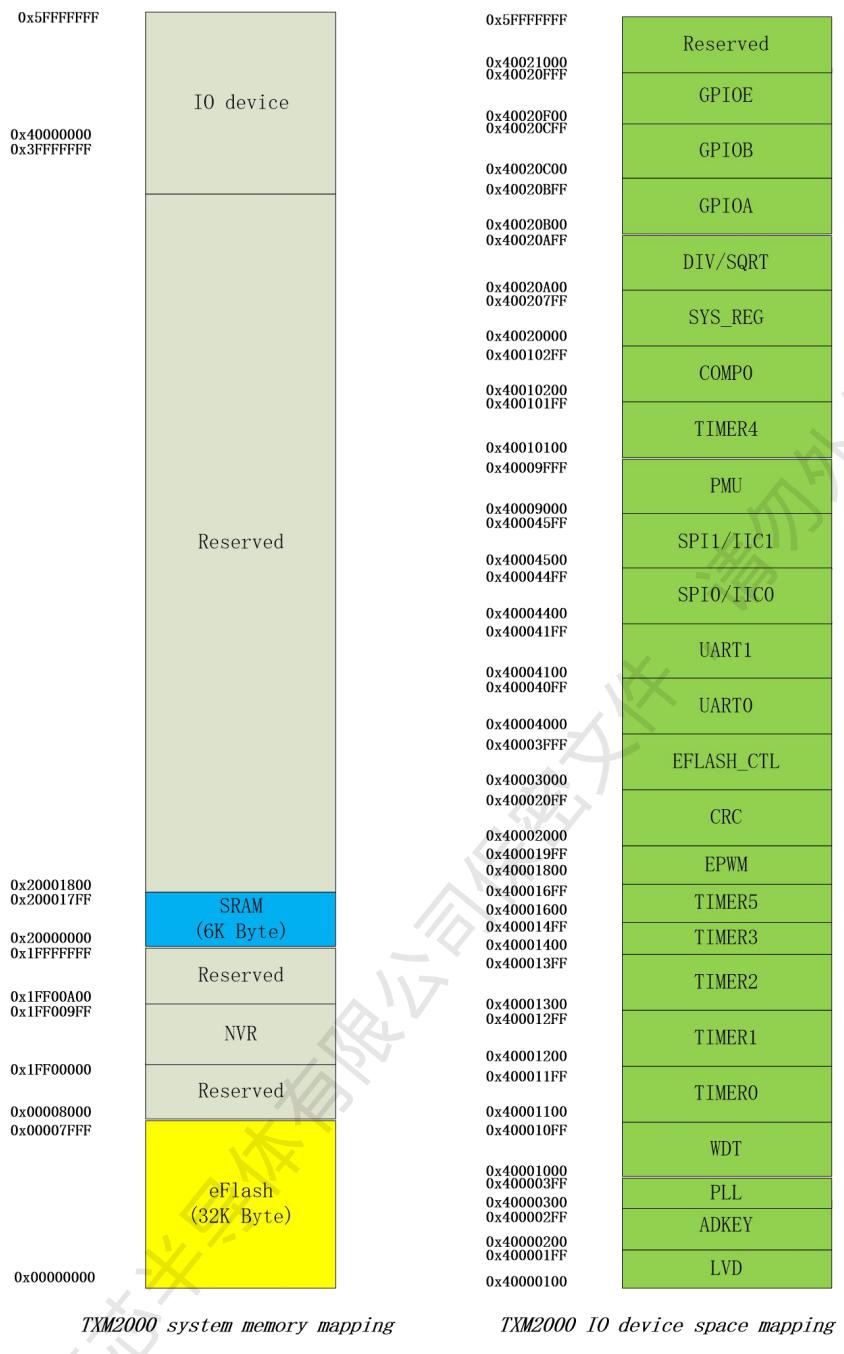

## 2.3. 存储器映射

此 32 位 RISC 处理器采用同一套总线来读取指令和加载/存储数据。指令代码和数据都位于相同的存储器地址空间，但在不同的地址范围。程序存储器，数据存储器，寄存器和 I/O 端口都在同一个线性的 4 GB 的地址空间之内。这是 32 位 RISC 的最大地址范围，因为它的地址总线宽度是 32 位。此外，为了降低不同客户在相同应用时的软件复杂度，存储映射是按 32 位 RISC 处理器提供的规则预先定义的。在存储器映射表中，一部分地址空间由 32 位 RISC 的系统外设所占用，且不可更改。此外，其余部分地址空间可由芯片供应商定义使用。

TX32M2300 系列器件的存储器映射表显示了 TX32M2300 系列器件的存储器映射，包括代码、SRAM、外设和其他预先定义的区域。简化了每个外设的地址译码。

图 2-2 TX32M2300 系列存储器映射表

### 2.3.1. 位带操作

为了减少“读-改-写”操作的次数，32 位 RISC 处理器提供了一个可以执行单原子比特操作的位带功能。存储器映射包含了两个支持位带操作的区域。其中一个是 SRAM 区的最低 1MB 范围，第二个是片内外设区的最低 1MB 范围。这两个区域中的地址除了普通应用外，还有自己的“位带别名区”。位带别名区把每个比特扩展成一个 32 位的字。当用户访问位带

别名区时，就可以达到访问原始比特的目的。

下面的公式表明了位带别名区中的每个字如何对应位带区的相应比特或目标比特。

$$\text{bit\_word\_addr} = \text{bit\_band\_base} + (\text{byte\_offset} \times 32) + (\text{bit\_number} \times 4) \quad (\text{式 3- 1})$$

其中：

- `bit_word_addr` 指的是位带区目标比特对应在位带别名区的地址；

- `bit_band_base` 指的是位带别名区的起始地址；

- `byte_offset` 指的是位带区目标比特所在的字节的字节地址偏移量；

- `bit_number` 指的是目标比特在对应字节中的位置(0-7)。

例如，要想访问 0x2000 0200 地址的第 7 位，可访问的位带别名区地址是：

$$\text{bit\_word\_addr} = 0x2200\ 0000 + (0x200 * 32) + (7 * 4) = 0x2200\ 401C \quad (\text{式 3- 2})$$

如果对 0x2200 401C 进行写操作，那么 0x2000 0200 的第 7 位将会相应变化；如果对 0x2200 401C 进行读操作，那么视 0x2000 0200 的第 7 位状态而返回 0x01 或 0x00。

### 2.3.2. 片上 SRAM 存储器

TX32M2300 系列内置最大可到 6K 字节的静态 SRAM。它可以以字节(8 位)、半字(16 位)或字(32 位)进行访问。SRAM 起始地址为 0x2000 0000。数据总线上最大可到 6K 字节的 SRAM。可以被 CPU 或者 DMA 用最快的系统时钟且不插入任何等待进行访问。DMA 支持访问外设有 timer5、ADC、CRC、SPI0/1、UART0/1、EFLASH。

### 2.3.3. 片上 FLASH 存储器概述

闪存存储器有两个不同存储区域：

- 主闪存存储块，它包括应用程序和用户数据区（若需要时）

- 信息块，其包含两个部分：

- 选项字节(Option bytes) — 内含硬件及存储保护用户配置选项。

- 系统存储器(System memory) — 其包含 Boot loader 代码。参见内置闪存存储器章节。

闪存接口基于 AHB 协议执行指令和数据存取。其预取缓冲的功能可加速 CPU 执行代码的速度。

### 2.3.4. 引导配置

芯片复位后，通过客户自己在主闪存存储块的配置，可选择启动模式 pin 脚为 PC6 还是 PC0，默认工作是上拉还是下拉。在启动延迟之后，CPU 从地址 0x0000 0000 获取堆栈顶的地址，并从启动存储器的 0x0000 0004 指示的地址开始执行代码。

内嵌的自举程序存放在系统存储器，由厂家在生产时写入。该程序可以通过 UART0 对闪存进行重新编程。

## 2.4. MCLR 功能

默认状态下 TX32M2300 系列支持 MCLR 复位功能的。MCLR 指在某个特定 IO 引脚上输入一个持续 1.7ms 以上的低电平导致系统复位，如同重新上电复位一样。当用户通过 eflash 中用户自定义 bit 来禁止使能 MCLR 功能后。PE2 会变成普通 IO 功能。详细情况请参考闪存存储器中关于用户自定义区域的描述。

## 3. 嵌入式闪存

### 3.1. 闪存主要特性

- 32K 字节闪存存储器

- 存储器结构：

- 主闪存空间：32K 字节

- 副闪存空间（系统存储器）：2K 字节

- 带预取缓冲器的读接口

- 闪存编程和擦除操作

- 访问和写保护

- 低功耗模式

### 3.2. 闪存功能描述

#### 3.2.1. 闪存结构

闪存空间由 32 位宽的存储单元组成，既可以存代码又可以存数据。主闪存块按 32 页（每页 1K 字节）分块，以页为单位设置写保护（参见存储保护相关内容）。

| 模块      | 名称            | 地址                        | 大小(字节) |

|---------|---------------|---------------------------|--------|

| 主闪存空间   | 页 0           | 0x0000_0000 - 0x0000_03FF | 1K     |

|         | 页 1           | 0x0000_0400 - 0x0000_07FF | 1K     |

|         | 页 2           | 0x0000_0800 - 0x0000_0BFF | 1K     |

|         | 页 3           | 0x0000_0C00 - 0x0000_0FFF | 1K     |

|         | ...           | ...                       | 1K     |

|         | 页 30          | 0x0000_7800 - 0x0000_7BFF | 1K     |

|         | 页 31          | 0x0000_7C00 - 0x0000_7FFF | 1K     |

|         |               |                           |        |

| 副闪存空间   | 扇区 0          | 0x1FF0_0000 - 0x1FF0_01FF | 512    |

|         | 扇区 1          | 0x1FF0_0200 - 0x1FF0_03FF | 512    |

|         | 扇区 2          | 0x1FF0_0400 - 0x1FF0_057F | 384    |

|         | 用户参数区         | 0x1FF0_0580 - 0x1FF0_06BF | 64     |

|         | 用户配置区         | 0x1FF0_05C0 - 0x1FF0_05FF | 64     |

|         | 芯片信息区         | 0x1FF0_0600 - 0x1FF0_064F | 80     |

|         | EOTP 芯片区域     | 0x1FF0_0650 - 0x1FF0_068F | 64     |

|         | EOTP 用户区域     | 0x1FF0_0690 - 0x1FF0_06EF | 96     |

| 闪存寄存器接口 | CTRLR0        | 0x4000_3000 - 0x4000_3003 | 4      |

|         | KST           | 0x4000_3004 - 0x4000_3007 | 4      |

|         | DONE          | 0x4000_3008 - 0x4000_300B | 4      |

|         | PROG_ADDR     | 0x4000_3010 - 0x4000_3013 | 4      |

|         | PROG_DATA     | 0x4000_3018 - 0x4000_301B | 4      |

|         | ERASE_CTRL    | 0x4000_3020 - 0x4000_3023 | 4      |

|         | TIME_REG0     | 0x4000_3030 - 0x4000_3033 | 4      |

|         | TIME_REG1     | 0x4000_3034 - 0x4000_3037 | 4      |

|         | NVR_PASSWORD  | 0x4000_3050 - 0x4000_3053 | 4      |

|         | MAIN_PASSWORD | 0x4000_3054 - 0x4000_3057 | 4      |

|         | CRC_ADDR      | 0x4000_3058 - 0x4000_305B | 4      |

|         | CRC_LEN       | 0x4000_305C - 0x4000_305F | 4      |

|         | CRC_OUT       | 0x4000_3060 - 0x4000_3063 | 4      |

### 3.2.2. 闪存读保护

读操作在整个产品工作电压范围内都可以完成，用于存放指令或者数据，Flash运行在36MHz的工作频率上，若工作频率提升到36MHz以上，需要让Flash的读时序执行分频。

芯片带有cache缓冲区和预取缓冲区，提升Flash的访问效率。

若用户配置区打开保护的配置后，当SWD等Debug接口连接上时，会自动对Flash执行保护机制。

读操作有下列2个寄存器完成：

- ①配置寄存器 (CTRLR0)

- ②时序0寄存器 (TIME\_REG0)

### 3.2.3. 闪存烧写和擦除操作

烧写和擦除操作在整个产品工作电压范围内都可以完成。

烧写和擦除操作有下列 6 个寄存器完成，先根据烧写的时钟配置好烧写时序 (TIME\_REG1)，再配置烧写密码，配置好编程地址，最后配置好编程数据，即可开始执行烧写，然后等烧写结束。

只要 CPU 不去访问 Flash 空间，或者访问 Flash 时已经 cache 命中，进行中的 Flash 写操作不会妨碍 CPU 的运行。也就是说，在对 Flash 进行写/擦除操作的同时，任何对 Flash 的访问都会令总线停顿，直到写/擦除操作完成后才会继续执行，这意味着在写/擦除 Flash 的同时不可以对它取指和访问数据

## 3.3. 寄存器

### 3.3.1. 寄存器基址

| Name   | Base Address | Description |

|--------|--------------|-------------|

| Eflash | 0x40003000   | Eflash 的基地址 |

### 3.3.2. 寄存器列表

| Offset Address | Name                | Description           |

|----------------|---------------------|-----------------------|

| 0x0            | EFLASH_CTRLR0       | 控制寄存器                 |

| 0x4            | EFLASH_KST          | 触发寄存器                 |

| 0x8            | EFLASH_DONE         | 状态寄存器                 |

| 0x10           | EFLASH_PROGADDR     | 编程地址寄存器               |

| 0x18           | EFLASH_PROGDATA     | 编程数据寄存器               |

| 0x20           | EFLASH_ERASECTRL    | 擦除控制寄存器               |

| 0x24           | EFLASH_INTFERASEENA | 中断打断 EFlash 工作状态控制寄存器 |

| 0x30           | EFLASH_TIMEREG0     | 时序 0 配置寄存器            |

| 0x34           | EFLASH_TIMEREG1     | 时序 1 配置寄存器            |

| 0x50           | EFLASH_NVRPASSWORD  | NVR 区域秘钥寄存器           |

|      |                     |              |

|------|---------------------|--------------|

| 0x54 | EFLASH_MAINPASSWORD | Main 区域秘钥寄存器 |

| 0x58 | EFLASH_CRCADDR      | CRC 地址寄存器    |

| 0x5C | EFLASH_CRCLEN       | CRC 长度寄存器    |

| 0x60 | EFLASH_CRCOUT       | CRC 输出寄存器    |

### 3.3.3. 寄存器详细说明

#### 3.3.3.1. EFLASH\_CTRLR0

| Bit(s) | Name                  | Description                                                                                                                               | R/W | Reset |

|--------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 31:20  | Reserved              |                                                                                                                                           | RO  | 0     |

| 19     | Error Interrupt IE    | <b>异常中断的使能位</b><br>使能该中断后，以下异常都会触发：<br>①非对齐地址编程<br>②编程数据错误<br>③无写权限<br>④擦除失败                                                              | RW  | 0     |

| 18     | Normal Interrupt IE   | <b>正常功能的中断使能位</b><br>使能该中断，以下情况会触发：<br>①编程<br>②擦除<br>③CRC 校验<br>④自动编程                                                                     | RW  | 0     |

| 17     | Reserved              |                                                                                                                                           | RO  | 0     |

| 16     | Program Clock select  | <b>Eflash 烧写时钟源选择，推荐使用 RC 时钟</b><br>0x0: 高速 RC 时钟 2 分频<br>0x1: 晶振，若 RC 不准时才使用                                                             | RW  | 0     |

| 15:12  | Reserved              |                                                                                                                                           | RO  | 0     |

| 11     | LVD Program Disable   | <b>LVD 掉电烧录控制位</b><br>在 LVD 断电时，是否允许打断 eflash program 和 erase，一般在断电时，立刻把重要数据保存在 eflash 上，就打开此功能，用于快速让 eflash 处于空闲状态<br>0x0: 关闭<br>0x1: 打开 | RW  | 0     |

| 10:6   | Reserved              |                                                                                                                                           | RO  | 0     |

| 5      | Block request Mode    | <b>Program/Erase 的请求缓冲模式（测试使用）</b><br>0x0: 关闭<br>0x1: 打开                                                                                  | RW  | 0     |

| 4      | Cache Write Back Mode | <b>Program/Sector Erase 自动回写到 cache（测试使用）</b>                                                                                             | RW  | 1     |

|   |                 |                                        |    |   |

|---|-----------------|----------------------------------------|----|---|

|   |                 | 0x0: 关闭<br>0x1: 打开                     |    |   |

| 3 | Reserved        |                                        | RO | 1 |

| 2 | Prefetch Enable | <b>预取使能位</b><br>0x0: 关闭<br>0x1: 打开     | RW | 0 |

| 1 | Reserved        |                                        | RO | 0 |

| 0 | Cache Enable    | <b>Cache 使能位</b><br>0x0: 关闭<br>0x1: 打开 | RW | 0 |

### 3.3.3.2. EFLASH\_KST

| Bit(s) | Name                        | Description                                                       | R/W | Reset |

|--------|-----------------------------|-------------------------------------------------------------------|-----|-------|

| 31     | EFLASH Error Clear Enable   | <b>异常标志清除使能位</b><br>注意：需要与 BIT[15]同时配置才有效<br>0x0: 关闭<br>0x1: 打开   | WO  | 0     |

| 30     | EFLASH Pending Clear Enable | <b>完成状态标志清除使能位</b><br>注意：需要与 BIT[14]同时配置才有效<br>0x0: 关闭<br>0x1: 打开 | WO  | 0     |

| 29:27  | Reserved                    |                                                                   | RO  | 0     |

| 26     | CRC Kick Enable             | <b>CRC 触发使能位</b><br>注意：需要与 BIT[10]同时配置才有效<br>0x0: 关闭<br>0x1: 打开   | WO  | 0     |

| 25     | Auto Program EFLASH Enable  | <b>自动编程使能位</b><br>注意：需要与 BIT[9]同时配置才有效<br>0x0: 关闭<br>0x1: 打开      | WO  | 0     |

| 24     | Auto Program RAM Enable     | <b>SRAM 自动编程使能位</b><br>注意：需要与 BIT[8]同时配置才有效<br>0x0: 关闭<br>0x1: 打开 | WO  | 0     |

| 23:21  | Reserved                    |                                                                   | RO  | 0     |

| 20     | Cache Clear Kick Enable     | <b>Cache 清除使能位</b><br>注意：需要与 BIT[4]同时配置才有效<br>0x0: 关闭<br>0x1: 打开  | WO  | 0     |

| 19:11  | Reserved                    |                                                                   | RO  | 0     |

| 15     | EFLASH Error Clear          | <b>异常标志清除位</b><br>注意：需要与 BIT[31]同时配置才有效<br>写 1 清除                 | WO  | 0     |

| 14     | EFLASH Pending Clear        | <b>完成状态标志清除位</b>                                                  | WO  | 0     |

|       |                                |                                                                  |    |   |

|-------|--------------------------------|------------------------------------------------------------------|----|---|

|       |                                | 注意：需要与 BIT[14]同时配置才有效<br>写1清除                                    |    |   |

| 13:11 | Reserved                       |                                                                  | RO | 0 |

| 10    | CRC Kick Start                 | <b>CRC 触发位</b><br>注意：需要与 BIT[26]同时配置才有效<br>0x0：关闭<br>0x1：打开      | WO | 0 |

| 9     | Auto Program EFLASH Kick start | <b>自动编程触发位</b><br>注意：需要与 BIT[25]同时配置才有效<br>0x0：关闭<br>0x1：打开      | WO | 0 |

| 8     | Auto Program RAM Kick start    | <b>SRAM 自动编程触发位</b><br>注意：需要与 BIT[24]同时配置才有效<br>0x0：关闭<br>0x1：打开 | WO | 0 |

| 7:5   | Reserved                       |                                                                  | RO | 0 |

| 4     | Cache Clear Kick Start         | <b>Cache 清除位</b><br>注意：需要与 BIT[20]同时配置才有效<br>0x0：关闭<br>0x1：打开    | WO | 0 |

| 3:0   | Reserved                       |                                                                  | RO | 0 |

### 3.3.3.3. EFLASH\_DONE

| Bit(s) | Name                   | Description                                                              | R/W | Reset |

|--------|------------------------|--------------------------------------------------------------------------|-----|-------|

| 31     | EFLASH Error           | <b>Error 状态标志位</b><br>0x0：正常<br>0x1：异常                                   | RO  | 0     |

| 30:20  | Reserved               |                                                                          | RO  | 0     |

| 19     | Chip Erase Error       | <b>全片擦除异常状态</b><br>0x0：工作正常<br>0x1：擦除异常，error 有效                         | RO  | 0     |

| 18     | Write permission Error | <b>编程权限异常状态</b><br>0x0：工作正常<br>0x1：无编程权限，error 有效                        | RO  | 0     |

| 17     | Program Address Error  | <b>编程地址异常状态</b><br>0x0：工作正常<br>0x1：非对齐地址，error 有效                        | RO  | 0     |

| 16     | Program Data Error     | <b>编程数据异常状态</b><br>已经编程的数据是否和软件配置的数据一致<br>0x0：工作正常<br>0x1：数据不一致，error 有效 | RO  | 0     |

| 15     | EFLASH Busy            | Eflash 工作状态标志                                                            | RO  | 0     |

|       |                          |                                                   |    |   |

|-------|--------------------------|---------------------------------------------------|----|---|

|       |                          | 0x0: 空闲状态<br>0x1: 进行中                             |    |   |

| 14:11 | Reserved                 |                                                   | RO | 0 |

| 10    | CRC Done                 | <b>CRC 完成标志</b><br>0: 进行中<br>1: 空闲状态              | RO | 1 |

| 9     | Auto Program EFLASH Done | <b>自动编程 eflash 完成标志</b><br>0x0: 空闲<br>0x1: 结束     | RO | 0 |

| 8     | Auto Program RAM Done    | <b>自动编程 RAM 完成标志</b><br>0x0: 空闲<br>0x1: 结束        | RO | 0 |

| 7     | Reserved                 |                                                   | RO | 0 |

| 6     | Program Done             | <b>Program 结束标志</b><br>0x0: 进行中<br>0x1: 空闲状态      | RO | 1 |

| 5     | Reserved                 |                                                   | RO | 0 |

| 4     | Cache Clear Done         | <b>Cache 初始化标志</b><br>0x0: 进行中<br>0x1: 空闲状态       | RO | 1 |

| 3:2   | Reserved                 |                                                   | RO | 0 |

| 1     | Chip Erase Done          | <b>Main 区域全擦除标志</b><br>0x0: 正在运行<br>0x1: 空闲状态     | RO | 1 |

| 0     | Sector Erase Done        | <b>扇区(512 byte)擦除标志</b><br>0x1: 正在运行<br>0x0: 空闲状态 | RO | 1 |

### 3.3.3.4. EFLASH\_PROGADDR

| Bit(s) | Name               | Description                                                                                                                                                          | R/W | Reset |

|--------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 31:30  | Program Byte       | <b>编程的位宽设置</b><br>eflash 通过功能区的 DATA RAM 设置, 分为 code 区域和 RAM 区域, 其中 RAM 区域可以执行 1/2/4 byte 的编程, 而 code 区域只能执行 4 byte 的编程<br>0x0: 1 byte<br>0x1: 2 byte<br>0x2: 4 byte | RW  | -     |

| 29     | Program NVR Select | <b>编程的地址是否 NVR 区域</b><br>0x0: MAIN 区域<br>0x1: NVR 区域                                                                                                                 | RW  | -     |

| 28:0   | Program Address    | <b>eflash 编程的地址</b><br>在自动编程模式下, 作为目的地址:<br>在自动编程 RAM 模式下, 此地址作为 RAM 地址;                                                                                             | RW  | -     |

|  |  |                                                                                                                                                                                                                            |  |  |

|--|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|  |  | <p>在自动编程 EFLASH 模式下, 此地址作为 EFLASH 地址。</p> <p>在 code 区域里编程:</p> <p>仅支持 4 byte 编程</p> <p>在 DATARAM 区域里编程:</p> <p>编程地址为 half word 对齐, 支持 1/2 byte 编程</p> <p>编程地址为 word 对齐, 支持 1/2/4 byte 编程</p> <p>编程地址为奇数, 仅支持 1 byte 编程</p> |  |  |

|--|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

### 3.3.3.5. EFLASH\_PROGDATA

| Bit(s) | Name         | Description               | R/W | Reset |

|--------|--------------|---------------------------|-----|-------|

| 31:0   | Program Data | eflash 编程的数据, 需要配置好地址才可进行 | RW  | 0     |

### 3.3.3.6. EFLASH\_ERASECTRL

| Bit(s) | Name                    | Description                                 | R/W | Reset |

|--------|-------------------------|---------------------------------------------|-----|-------|

| 31     | Chip Erase Kick Start   | Chip 全擦除的触发<br>写“1”触发, 需要先配置密码              | RO  | 0     |

| 30     | Sector Erase Kick Start | Sector 擦除的触发<br>写“1”触发, 需要先配置密码             | RO  | 0     |

| 29     | NVR Sector Enable       | NVR 的 sector 使能位<br>0: MAIN 区域<br>1: NVR 区域 | RW  | 0     |

| 28:7   | Reserved                |                                             | RO  | 0     |

| 6:0    | Erase Sector Address    | 擦除的 sector 选择, 范围 0-127                     | RW  | 0     |

### 3.3.3.7. EFLASH\_TIMEREG0

| Bit(s) | Name     | Description                                                         | R/W | Reset |

|--------|----------|---------------------------------------------------------------------|-----|-------|

| 31:20  | Reserved |                                                                     | RO  | 0     |

| 19:16  | PGH      | WEB low to PROG2 high hold min time is 15ns                         | RW  | 1     |

| 15:12  | ADS      | BYTE/Address/data setup min time is 15ns                            | RW  | 1     |

| 11:8   | ADH      | BYTE/Address/data hold min time is 15ns                             | RW  | 1     |

| 7:4    | RW       | Latency to next operation after PROG/ERASE<br>low min time is 100ns | RW  | 8     |

| 3:0    | RC       | Read Cycle Min Time is 25/30ns                                      | RW  | 0     |

### 3.3.3.8. EFLASH\_TIME\_REG1

| Bit(s) | Name | Description | R/W | Reset |

|--------|------|-------------|-----|-------|

|--------|------|-------------|-----|-------|

|       |          |                         |    |      |

|-------|----------|-------------------------|----|------|

| 31:20 | Reserved |                         | RO | 0    |

| 18:8  | 1ms unit | 1ms 的时间配置值, 以 1us 为单位   | RW | 1000 |

| 7:0   | 1us unit | 1us 的时间配置值, 系统默认是 26MHz | RW | 26   |

### 3.3.3.9. EFLASH\_NVR\_PASSWORD

| Bit(s) | Name         | Description                              | R/W | Reset |

|--------|--------------|------------------------------------------|-----|-------|

| 31:10  | NVR password | 密码为 0x20150931, 只有打开密码后, 才能对 NVR 进行擦除和编程 | RW  | 0     |

### 3.3.3.10. EFLASH\_MAIN\_PASSWORD

| Bit(s) | Name          | Description                               | R/W | Reset |

|--------|---------------|-------------------------------------------|-----|-------|

| 31:10  | Main password | 密码为 0x20170230, 只有打开密码后, 才能对 Main 进行擦除和编程 | RW  | 0     |

### 3.3.3.11. EFLASH\_CRC\_ADDR

| Bit(s) | Name        | Description                                                                                | R/W | Reset |

|--------|-------------|--------------------------------------------------------------------------------------------|-----|-------|

| 31:30  | Reserved    |                                                                                            | RO  | 0     |

| 29     | NVR Select  | 地址是否 NVR 区域<br>0x0: MAIN 区域<br>0x1: NVR 区域                                                 | RW  | 0     |

| 28:2   | DMA Address | CRC DMA 的开始地址, 作为源地址<br>在自动编程 RAM 模式下, 此地址作为 EFLASH 地址;<br>在自动编程 EFLASH 模式下, 此地址作为 RAM 地址。 | RW  | 0     |

| 1:0    | Reserved    | 保留, 低 2 位地址固定为 0, word 对齐                                                                  | RO  | 0     |

### 3.3.3.12. EFLASH\_CRC\_LEN

| Bit(s) | Name       | Description               | R/W | Reset |

|--------|------------|---------------------------|-----|-------|

| 31:2   | DMA length | CRC DMA 的长度               | RW  | 0     |

| 1:0    | Reserved   | 保留, 低 2 位地址固定为 0, word 对齐 | RO  | 0     |

### 3.3.3.13. EFLASH\_CRC\_OUT

| Bit(s) | Name       | Description                            | R/W | Reset |

|--------|------------|----------------------------------------|-----|-------|

| 31:00  | CRC Result | CRC 结果输出<br>多项式 CRC-32 如下, 出来的结果取反就是官方 | RO  | 0     |

|  |  |                                                                                             |  |  |

|--|--|---------------------------------------------------------------------------------------------|--|--|

|  |  | 的结果，写入 EFLASH 的 CRC 需要官方的值取反表示！！！<br>x32+x26+x23+x22+x16+x12+x11+x10+x8+x7+x5<br>+x4+x2+x+1 |  |  |

|--|--|---------------------------------------------------------------------------------------------|--|--|

## 4. 中断和事件

### 4.1. 嵌套向量中断控制器

基本功能：

- 中断都可屏蔽（除了 NMI）

- 16 个可编程的优先等级（使用了 4 位中断优先级）

- 低延迟的异常和中断处理

- 电源管理控制

- 系统控制寄存器的实现

嵌套向量中断控制器（NVIC）和处理器核的接口紧密相连，可以实现低延迟的中断处理和高效地处理晚到的中断。

嵌套向量中断控制器管理着包括核异常等中断。关于更多的异常和 NVIC 编程的说明请参考 CPU 技术参考手册。

### 4.2. 系统嘀嗒（SysTick）校准值寄存器

本芯片不支持使用外部时钟计时 1ms。

### 4.3. 中断功能描述

处理器和嵌套式矢量型中断控制器(NVIC)在处理(Handler)模式下对所有异常进行优先级区分以及处理。当异常发生时，系统自动将当前处理器工作状态压栈，在执行完中断服务子程序 (ISR) 后自动将其出栈。

取向量是和当前工作态压栈并行进行的，从而提高了中断入口效率。处理器支持咬尾中断，可实现背靠背中断，大大削减了反复切换工作态所带来的开销。NVIC 异常类型列出了所有的异常类型。

表 4-1 CPU 中的 NVIC 异常类型

| 异常类型         | 向量号  | 优先级 | 向量地址                  | 描述                |

|--------------|------|-----|-----------------------|-------------------|

| -            | 0    | -   | 0x00000000            | 保留                |

| 复位           | 1    | -3  | 0x00000004            | 复位                |

| NMI          | 2    | -2  | 0x00000008            | 不可屏蔽中断            |

| HardFault    | 3    | -1  | 0x0000000C            | 各种硬件级别故障          |

| MemManage    | 4    | 可设置 | 0x00000010            | 存储器管理             |

| BusFault     | 5    | 可设置 | 0x00000014            | 预取指故障，存储器访问故障     |

| UsageFault   | 6    | 可设置 | 0x00000018            | 未定义的指令或者非法状态      |

| -            | 7-10 | -   | 0x0000001C-0x0000002B | 保留                |

| SVcall       | 11   | 可设置 | 0x0000002C            | 通过 SWI 指令实现系统服务调用 |

| DebugMonitor | 12   | 可设置 | 0x00000030            | 调试监控器             |

| -            | 13   | -   | 0x00000034            | 保留                |

| PendSV       | 14   | 可设置 | 0x00000038            | 可挂起的系统服务请求        |

| Systick      | 15   | 可设置 | 0x0000003C            | 系统节拍定时器           |

SysTick 校准值设为 0x1196E，SysTick 时钟频率配置为 HCLK，此时若 HCLK 时钟被配置为 72MHz，则 SysTick 中断会 1ms 响应一次。

表 4-2 中断向量表

| 中断序号  | 向量号 | 外设中断描述          | 向量地址        |

|-------|-----|-----------------|-------------|

| IRQ0  | 16  | lvd_int         | 0x0000_0040 |

| IRQ1  | 17  | uart0_int       | 0x0000_0044 |

| IRQ2  | 18  | uart1_int       | 0x0000_0048 |

| IRQ3  | 19  | spi0_int        | 0x0000_004C |

| IRQ4  | 20  | spil_int        | 0x0000_0050 |

| IRQ5  | 21  | gpioa_int       | 0x0000_0054 |

| IRQ6  | 22  | gpiob_int       | 0x0000_0058 |

| IRQ7  | 23  | gpioe_int       | 0x0000_005C |

| IRQ8  | 24  | wkpnd_int       | 0x0000_0060 |

| IRQ9  | 25  | timer0_int      | 0x0000_0064 |

| IRQ10 | 26  | timer1_int      | 0x0000_0068 |

| IRQ11 | 27  | timer2_int      | 0x0000_006C |

| IRQ12 | 28  | timer3_int      | 0x0000_0070 |

| IRQ13 | 29  | timer4_int      | 0x0000_0074 |

| IRQ14 | 30  | timer5_int      | 0x0000_0078 |

| IRQ15 | 31  | epwm_tzint      | 0x0000_007C |

| IRQ16 | 32  | epwm_etint      | 0x0000_0080 |

| IRQ17 | 33  | adkey_interrupt | 0x0000_0084 |

|       |    |               |             |

|-------|----|---------------|-------------|

| IRQ18 | 34 | div_ovf_int   | 0x0000_0088 |

| IRQ19 | 35 | crc_dma_int   | 0x0000_008C |

| IRQ20 | 36 | comp_int      | 0x0000_0090 |

| IRQ21 | 37 | wdt_interrupt | 0x0000_0094 |

| IRQ22 | 38 | eflash_int    | 0x0000_0098 |

| IRQ23 | 39 | adkey_int1    | 0x0000_009C |

| IRQ24 | 40 | -             | 0x0000_00A0 |

| IRQ25 | 41 | -             | 0x0000_00A4 |

| IRQ26 | 42 | -             | 0x0000_00A8 |

| IRQ27 | 43 | -             | 0x0000_00AC |

| IRQ28 | 44 | -             | 0x0000_00B0 |

| IRQ29 | 45 | -             | 0x0000_00B4 |

| IRQ30 | 46 | -             | 0x0000_00B8 |

| IRQ31 | 47 | -             | 0x0000_00BC |

## 4.4. 外部中断/事件控制器（EXTI）

外部中断和时间控制器（EXTI）管理外部和内部异步事件/中断，并生成相应的事件请求到 CPU/中断控制器和到电源管理的唤醒请求。每个输入线可以独立地配置输入类型（脉冲或挂起）和对应的触发事件（上升沿或下降沿或者双边沿都触发）。每个输入线都可以独立地被屏蔽。挂起寄存器保持着状态线的中断请求。

### 4.4.1. 主要特征

EXTI 控制器的主要特性如下：

- 每个中断/事件都有独立的触发和屏蔽

- 每个中断线都有专用的状态位

- 支持多达 20 个软件的中断/事件请求

- 检测脉冲宽度低于 APB0 时钟宽度的外部信号

参见数据手册中电气特性部分的相关参数

#### 4.4.2. 唤醒事件管理

TX32M2300 系列可以处理外部或内部事件来唤醒内核（WFE）。唤醒事件可以通过下述配置产生：

- 外设的控制寄存器使能一个中断，但不在 NVIC 中使能，同时在 CPU 的系统控制寄存器中使能 SEVONPEND 位。当 CPU 从 WFE 恢复后，需要清除相应外设的中断挂起位和外设 NVIC 中断通道挂起位（在 NVIC 中断清除挂起寄存器中）。

- 配置一个外部或内部 EXTI 线为事件模式，当 CPU 从 WFE 恢复后，因为对应事件线的挂起位没有被置位，不必清除相应外设的中断挂起位或 NVIC 中断通道挂起位。

### 5. 电源控制

#### 5.1. 电源

芯片的工作电压（VCC）为 2.0V ~ 5.5V。本芯片采用 CAPLESS 设计，无需在内置 LDO 输出上外挂电容。

##### 5.1.1. 电压调节器

复位后调节器总是使能的。在需要低功耗的场合，可以使能低功耗工作模式，PMUCON0.ipen 做为功耗模式切换控制位。

## 5.2. 电源管理器

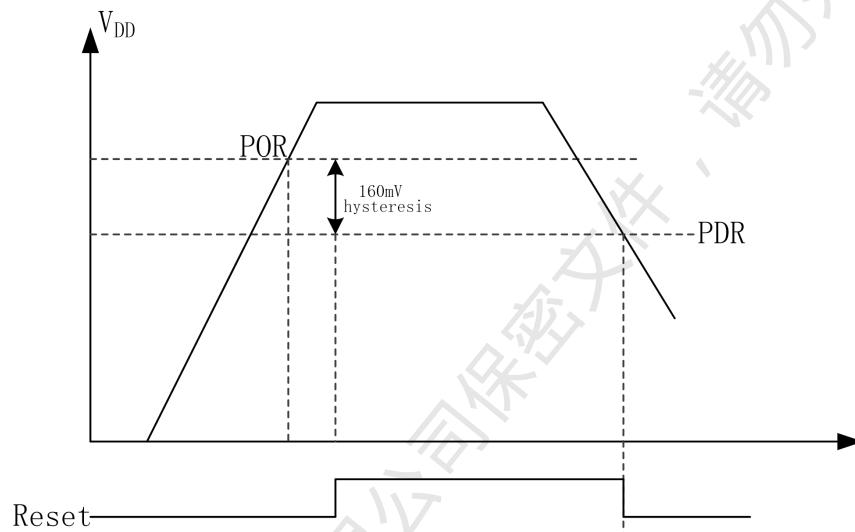

### 5.2.1. 上电复位 (POR) 和掉电复位 (PDR)

TX32M2300 系列内部有一个完整的上电复位 (POR) 和掉电复位 (PDR) 电路，当供电电压达到 2.7V

时系统既能正常工作。当 VDD 低于指定的限位电压 VPOR/VPDR 时，系统保持为复位状态，而无需外部复位电路。

图 6-1 上电复位和掉电复位

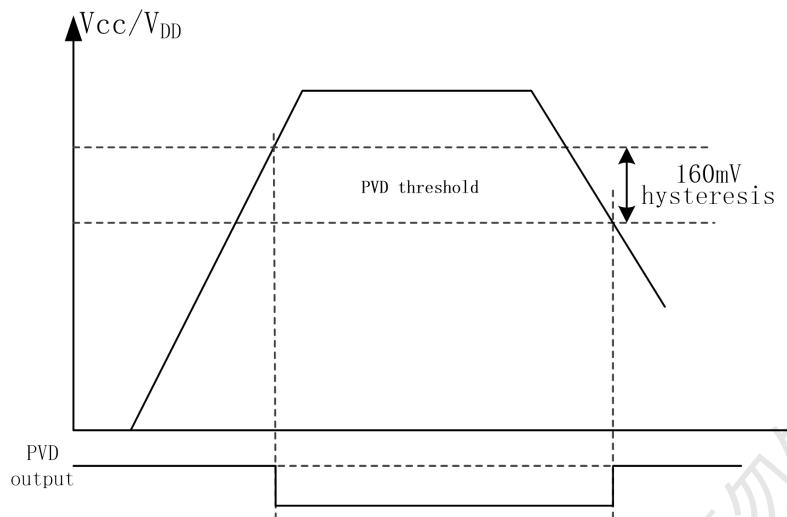

### 5.2.2. 可编程电压监测器 (PWD)

TX32M2300 系列内部集成两个电压检测器，一个检测外部供电 VCC, 一个检测内部 LDO 输出 VDD，LDO 采样 capless 结构，封装上 VDD 不可见。两种检测电压均阈值可选。当系统监测到 VCC 或 VDD 电压低于配置电压值时，可以选择触发系统复位或通过使能 PVD 中断进入中断子函数。这一特性可用于用于执行紧急关闭任务。检测信号可以选择经过毛刺滤波电路或直接检测，由 LVD\_CON.lvdvcc\_bps\_en 和 LVD\_CON.lvdvdd\_bps\_en 来控制。

图 6-2 PVD 示意图

### 5.3. 低功耗模式

在系统或电源复位以后，微控制器处于运行状态，系统所用时钟为 256Khz 内部 RC。当 CPU 不需继续运行时，可以利用多种低功耗模式来节省功耗，例如等待某个外部事件时。用户需要根据最低电源消耗、最快速启动时间和可用的唤醒源等条件，选定一个最佳的低功耗模式。

TX32M2300 系列有三种低功耗模式：

- IDLE 模式（CPU 停止，所有外设包括 CPU 的外设，如 NVIC、系统时钟（SysTick）等仍在运行）

- STOP 模式（CPU，大部分外设停止，可依赖其他时间唤醒此模式后芯片继续运行）

- SLEEP 模式（所有时钟源都停止，依赖外部 IO 唤醒，可以选择复位芯片或继续运行）

此外，在运行模式下，可以通过以下方式中的一种降低功耗：

- 降低系统时钟

- 关闭 APB 和 AHB 总线上未被使用的外设时钟

- 合理配置 APB 与 AHB 的频率关系

## 5.4. 寄存器

### 5.4.1. 寄存器地址

| Name | Base Address | Description |

|------|--------------|-------------|

| LVD  | 0x40000100   | LVD 的基址     |

### 5.4.2. 寄存器列表

| Offset Address | Name    | Description |

|----------------|---------|-------------|

| 0x00           | LVD_CON | 配置寄存器       |

### 5.4.3. 寄存器详细说明

#### 5.4.3.1. LVD\_CON

| Bit(s) | Name            | Description                                                | R/W | Reset |

|--------|-----------------|------------------------------------------------------------|-----|-------|

| 31     | lvdvdd_pending  | VDD 电压低于设定阈值触发 pending<br>write 0 clean this bit           | R   | 0     |

| 30     | lvdvcc_pending  | VCC 电压低于设定阈值触发 pending<br>write 0 clean this bit           | R   | 0     |

| 29     | Reserved        |                                                            | -   | -     |

| 28:22  | dbs_lo_limit    | 滤波检测电压信号低毛刺宽度<br>单位为 LVDBS_CLK                             | RW  | 0     |

| 21:15  | dbs_hi_limit    | 滤波检测电压信号高毛刺宽度<br>单位为 LVDBS_CLK                             | RW  | 0     |

| 14     | lvdvcc_sync_dis | 检测到VCC 低电压信号触发 LVDVCC 低电唤醒源是否需要同步<br>0x0: 需要同步<br>0x1: 不同步 | RW  | 0     |

| 13     | lvdvdd_bps_en   | 使能采样 debounce 后的 VDD 电压状态信号<br>0x0: 关闭<br>0x1: 打开          | RW  | 0     |

| 12     | lvdvcc_bps_en   | 使能采样 debounce 后的 VCC 电压状态信号<br>0x0: 关闭<br>0x1: 打开          | RW  | 0     |

| 11     | lvd_oe          | 使能阈值判断触发条件后中断, 以及复位功能<br>0x0: 关闭                           | RW  | 1     |

|     |               |                                                                                                                                                                                                                                                                                                                                                                               |    |     |

|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

|     |               | 0x1: 打开                                                                                                                                                                                                                                                                                                                                                                       |    |     |

| 10  | lvdvdd_RST_en | <b>VDD 阈值判断触发后复位系统使能</b><br>0x0: 中断, 不复位<br>0x1: 复位, 不中断                                                                                                                                                                                                                                                                                                                      | RW | 1   |

| 9   | lvdvcc_RST_en | <b>VCC 阈值判断触发后复位系统使能</b><br>0x0: 中断, 不复位<br>0x1: 复位, 不中断                                                                                                                                                                                                                                                                                                                      | RW | 1   |

| 8:4 | hlvd_s        | <b>VCC LVD 档位设置</b><br>0x00: 1. 7<br>0x01: 1. 8<br>0x02: 1. 9<br>0x03: 2<br>0x04: 2. 1<br>0x05: 2. 2<br>0x06: 2. 3<br>0x07: 2. 4<br>0x08: 2. 55<br>0x09: 2. 65<br>0x0A: 2. 8<br>0x0B: 2. 95<br>0x0C: 3. 1<br>0x0D: 3. 25<br>0x0E: 3. 4<br>0x0F: 3. 55<br>0x10: 3. 35<br>0x11: 3. 55<br>0x12: 3. 75<br>0x13: 3. 95<br>0x14: 4. 15<br>0x15: 4. 35<br>0x16: 4. 55<br>0x17: 4. 75 | RW | 0x9 |

| 3:2 | llvd_s        | <b>VDD LVD 档位设置</b><br>0x0: 0. 99<br>0x1: 1. 09<br>0x2: 1. 19<br>0x3: 1. 29                                                                                                                                                                                                                                                                                                   | RW | 0x2 |

| 1   | llvd_en       | <b>VDD LVD 使能位</b><br>0x0: 关闭<br>0x1: 打开                                                                                                                                                                                                                                                                                                                                      | RW | 1   |

| 0   | hlvd_en       | <b>VCC LVD 使能位</b><br>0x0: 关闭<br>0x1: 打开                                                                                                                                                                                                                                                                                                                                      | RW | 1   |

## 6. 复位和时钟控制

### 6.1. 复位

TX32M2300 系列支持电源复位和系统复位和主复位。

#### 6.1.1. 系统复位

系统复位将复位除某些复位状态寄存器和特殊功能寄存器之外的所有寄存器。

当以下事件中的一件发生时，产生一个系统复位：

SLEEP 模式下外部 IO 口/LVDVCC 低电/COMPO 唤醒；

WDT 计数溢出复位

系统复位请求复位

UART0 升级程序复位

系统锁定复位

### 6.2. 主复位

主复位能将部分系统复位无法复位的寄存器复位。

以下事件可以触发一个主复位：

软件复位

PVD 检测到电压低事件，且控制器处于复位功能模式

当芯片支持 MCLR 复位时，MCLR 脚上一个持续 1ms 以上的低电平，触发复位

#### 6.2.1. 电源复位

上电/掉电复位（POR/PDR 复位）都属于电源复位。电源复位将复位所有的逻辑和模拟模块。

复位入口矢量被固定在地址 0x0000\_0004。

## 6.3. 时钟

### 6.3.1. XOSC 时钟

高速外部时钟信号（XOSC）由以下两种时钟源产生：

- 外部晶体/陶瓷谐振器

- 用户外部时钟

### 6.3.2. HIRC 时钟

HIRC 时钟信号由内部 26MHz 的振荡器产生，可直接作为系统时钟或作为 PLL 输入。

HIRC 振荡器能够在不需要任何外部器件的条件下提供系统时钟。它的启动时间比 XOSC 晶体振荡器短。然而，即使在校准之后它的时钟频率精度仍较差。需要出厂时校准，校准值写在 flash 系统存储区域。可以程序在使用这个时钟前，可以读取并配置出高精度的 HIRC 时钟。经过出厂效验后，常温状态下 HIRC 精度为 26MHz(+/- 1.5%)。精确的频率在 0x1FF0\_0600 – 0x1FF0\_06FF 闪存区域有描述，用户可通过读取得到 HIRC 的精确频率。

如果 XOSC 晶体振荡器失效， HIRC 时钟会被作为备用时钟源。参考时钟安全系统（CSS）。

### 6.3.3. PLL

内部 PLL 可以用内部时钟源如 XOSC, HIRC 等做为参考，系统配置小数分频比得到想要的任意时钟频率，经过分频电路后可以作为系统时钟。

### 6.3.4. LIRC 时钟

LIRC 振荡器担当一个低功耗时钟源的角色，它作为系统启动时钟为看门狗和其他单元提供时钟。 LIRC 时钟频率大约 128KHz（在 90KHz 和 166KHz 之间）。进一步信息请参考数

据手册中有关电气特性部分。

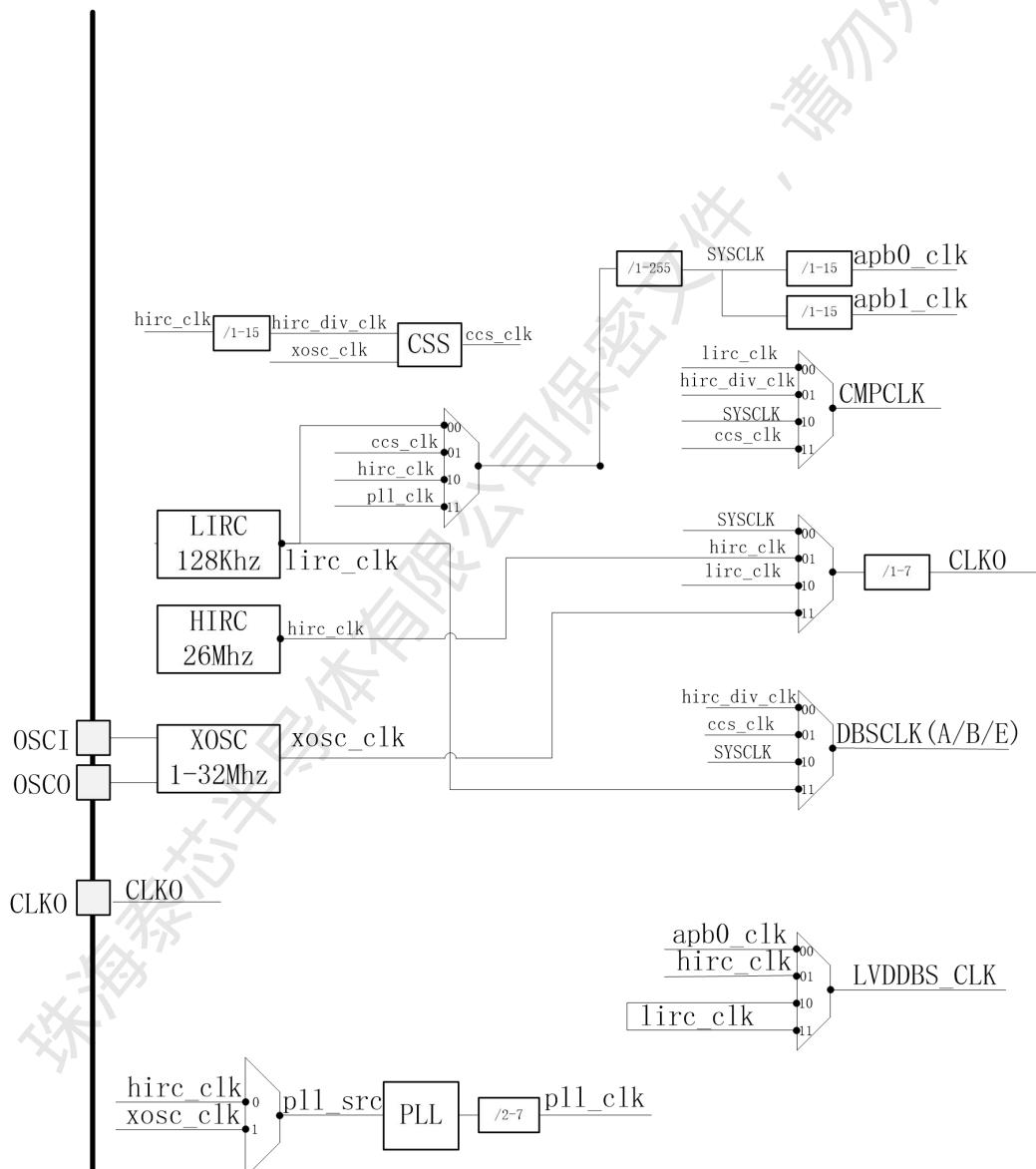

### 6.3.5. 系统时钟 (SYSCLK) 选择

四种不同的时钟源可被用来驱动系统时钟 (SYSCLK) :

- 内部低速 128Khz LIRC

- 内部高速 26Mhz HIRC

- 外部高速晶振 XOSC

- 片内高速 PLL 时钟

### 6.3.6. DBSCLK 选择

四种不同的时钟源可被用来驱动 GPIO 的 glitch debounce clock (DBSCLK) :

- 外部高速晶振 XOSC

- 内部高速 26Mhz HIRC 的分频时钟

- SYSCLK

- 内部低速 128Khz LIRC

### 6.3.7. LVDDBS\_CLK 时钟选择

四种不同的时钟源可被用来驱动 LVD VCC/VDD 的 debounce clock (LVDDBS\_CLK) , 独立于系统时钟而工作 :

- APB0CLK

- 内部高速 26Mhz HIRC 的分频时钟

- 内部低速 128Khz LIRC

- 外部高速晶振 XOSC

### 6.3.8. CMPCLK 时钟选择

四种不同的时钟源可被用来驱动 comparor 的 clock (CMPCLK) :

- 内部低速 128Khz LIRC

- 内部高速 26Mhz HIRC 的分频时钟

- 系统时钟

- 外部高速晶振 XOSC

当不被使用时，任一个时钟源都可被独立地启动或关闭，由此优化系统功耗。

图 7-1 时钟结构

### 6.3.9. 时钟安全系统 (CSS)

时钟安全系统可以通过软件被激活。在使用这个功能时,请确保 XOSC 已经被成功使能。如果 XOSC 时钟发生故障,产生时钟安全中断 CSSI,允许软件完成营救操作。此 CSSI 中断连接到 CPU 的 NMI 中断。注:一旦 CSS 被激活,并且 XOSC 时钟出现故障,CSS 中断就产生,并且 NMI 也自动产生。NMI 将被不断执行,直到 CSS 中断挂起位被清除。因此,在 NMI 的处理程序中必须通过设置时钟中断寄存器,(HOSC\_MNT) 里的 hosc\_loss\_pending 位写 1 来清除 CSS 中断。通过寄存器使能,时钟故障将导致内部 XOSC 时钟自动切换到 hirc\_div\_clk。

## 6.4. 寄存器

### 6.4.1. 寄存器基址

| Name   | Base Address | Description |

|--------|--------------|-------------|

| System | 0x40020000   | System 的基地址 |

### 6.4.2. 寄存器列表

表 7-1 寄存器列表

| Offset Address | Name     | Description  |

|----------------|----------|--------------|

| 0x0000         | SYS_KEY  | 系统配置 key 寄存器 |

| 0x0004         | SYS_CON0 | 系统控制寄存器 0    |

| 0x0008         | SYS_CON1 | 系统控制寄存器 1    |

| 0x000c         | SYS_CON2 | 系统控制寄存器 2    |

| 0x0010         | SYS_CON3 | 系统控制寄存器 3    |

| 0x0014         | SYS_CON4 | 系统控制寄存器 4    |

| 0x0018         | SYS_CON5 | 系统控制寄存器 5    |

| 0x001c         | SYS_CON6 | 系统控制寄存器 6    |

| 0x0020         | SYS_CON7 | 系统控制寄存器 7    |

| 0x0024         | CLK_CON0 | 时钟控制寄存器 0    |

| 0x0028         | CLK_CON1 | 时钟控制寄存器 1    |

| 0x002c         | CLK_CON2 | 时钟控制寄存器 2    |

|        |            |                             |

|--------|------------|-----------------------------|

| 0x0030 | CLK_CON3   | 时钟控制寄存器 3                   |

| 0x0034 | CLK_CON4   | 时钟控制寄存器 4                   |

| 0x0038 | CLK_CON5   | 时钟控制寄存器 5                   |

| 0x003c | CLK_CON6   | 时钟控制寄存器 6                   |

| 0x0040 | CLK_CON7   | 时钟控制寄存器 7                   |

| 0x0044 | HOSC_MNT   | XOSC 控制寄存器                  |

| 0x0048 | SYS_ERR    | 系统异常错误寄存器                   |

| 0x004c | WKUP_CON   | Wakeup 寄存器                  |

| 0x0050 | LP_CON     | 低功耗寄存器                      |

| 0x0054 | MBIST_CON  | Memory Bist 寄存器             |

| 0x0058 | MBIST_MISR | Memory Bist Rom result 寄存器  |

| 0x005c | RESERVED   |                             |

| 0x0060 | MODE       | 模式配置寄存器                     |

| 0x0064 | PMU_CON    | PMU 控制器                     |

| 0x0068 | RPCON      | System pending recording    |

| 0x006c | AMP_CON0   | AMP 控制寄存器 0                 |

| 0x0070 | AMP_CON1   | AMP 控制寄存器 1                 |

| 0x0074 | PMUBK      | PMU lower power mode backup |

### 6.4.3. 寄存器定义

#### 6.4.3.1. SYS\_KEY

| Bit(s) | Name    | Description                                                                                                                                  | R/W | Reset |

|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 31:0   | sys_key | 系统寄存器配置 key<br>写入 0x3fac87e4 使所有系统寄存器写入使能，<br>Setsys_keyother 值将清除此位 other 值将清除<br>此位。读取返回 sys_key 状态<br>0x0: 锁定所有系统寄存器写入<br>0x1: 解锁所有系统寄存器写 | RW  | 0x1   |

#### 6.4.3.2. SYS\_CON0

| Bit(s) | Name              | Description                                                                                                       | R/W | Reset |

|--------|-------------------|-------------------------------------------------------------------------------------------------------------------|-----|-------|

| 31     | fast_RST_en       | 快速复位使能<br>复位时间会在 1ms ~62us                                                                                        | R/W | 0x0   |

| 30     | sleep_goon_en     | 触发 wakeup 后，是否继续运行<br>0x0: 复位<br>0x1: 继续运行                                                                        | R/W | 0x0   |

| 29:27  | sleep_dly_cnt     | Wakeup 后延迟 goon 运行时间配置<br>0x0: two 128K RC cycles<br>0x1: three 128K RC cycles<br>...<br>0x7: nine 128K RC cycles | R/W | 0x0   |

| 26     | dbs_soft_RST_     | GPIO debounce 软件复位<br>先写 0, 后写 1 才能完成复位操作                                                                         | R/W | 0x1   |

| 25     | crc_soft_RST_     | CRC 软件复位<br>先写 0, 后写 1 才能完成复位操作                                                                                   | R/W | 0x1   |

| 24:21  | Reserved          |                                                                                                                   | R/W | 0xF   |

| 20     | gpio_soft_RST_    | GPIOA/GPIOB/GPIOE 软件复位<br>先写 0, 后写 1 才能完成复位操作                                                                     | R/W | 0x1   |

| 19     | adkey_soft_RST_   | ADCKey 软件复位<br>先写 0, 后写 1 才能完成复位操作                                                                                | R/W | 0x1   |

| 18     | uart1_soft_RST_   | UART1 软件复位<br>先写 0, 后写 1 才能完成复位操作                                                                                 | R/W | 0x1   |

| 17     | uart0_soft_RST_   | UART0 软件复位<br>先写 0, 后写 1 才能完成复位操作                                                                                 | R/W | 0x1   |

| 16     | spil_soft_RST_    | SPI1 软件复位<br>先写 0, 后写 1 才能完成复位操作                                                                                  | R/W | 0x1   |

| 15     | spi0_soft_RST_    | SPI0 软件复位<br>先写 0, 后写 1 才能完成复位操作                                                                                  | R/W | 0x1   |

| 14     | epwm_soft_RST_    | EPWM 软件复位<br>先写 0, 后写 1 才能完成复位操作                                                                                  | R/W | 0x1   |

| 13:9   | Reserved          |                                                                                                                   | R/W | 0x1F  |

| 8      | wdt_soft_RST_     | WDT 软件复位<br>先写 0, 后写 1 才能完成复位操作                                                                                   | R/W | 0x1   |

| 7      | wdt_SYS_soft_RST_ | WDT SYS 软件复位<br>先写 0, 后写 1 才能完成复位操作                                                                               | R/W | 0x1   |

| 6      | timer_soft_RST_   | TIMER 软件复位<br>先写 0, 后写 1 才能完成复位操作                                                                                 | R/W | 0x1   |

| 5:0    | Reserved          | For future usage                                                                                                  | R/W | 0x3F  |

#### 6.4.3.3. SYS\_CON1

| Bit(s) | Name | Description | R/W | Reset |

|--------|------|-------------|-----|-------|

|        |      |             |     |       |

|       |                   |                                                                                   |     |     |

|-------|-------------------|-----------------------------------------------------------------------------------|-----|-----|

| 31:14 | Reserved          |                                                                                   | -   | -   |

| 13    | uart_update_dis   | <b>串口单 pin 升级</b><br>0x0: 打开<br>0x1: 关闭                                           | R/W | 0x0 |

| 12    | debug_en          | <b>Sleep 模式与 debug 联动配置</b><br>Sleep、stopclk 模式将在调试连接时自动唤醒。<br>0x0: 打开<br>0x1: 关闭 | R/W | 0x0 |

| 11    | int_remap_en      | <b>中断入口地址重映射使能</b><br>0x0: EFLASH<br>0x1: SRAM                                    | R/W | 0x0 |

| 10    | nmi_inv_sel       | <b>NMI Pin 检测信号反转配置</b><br>0x0: 高电平触发 NMI<br>0x1: 低电平触发 NMI                       | R/W | 0x0 |

| 9     | cp_mode_sysclk_en | <b>CP 模式下切换系统时钟</b><br>0x0: 切换<br>0x1: 保持 ate-clk                                 | R/W | 0x1 |

| 8     | swd_en            | <b>SWD 使能</b><br>0x0: 关闭<br>0x1: 打开                                               | R/W | 0x1 |

| 7     | lvdvcc_wkup_en    | <b>VCC LVD 唤醒使能</b><br>0x0: 关闭<br>0x1: 打开                                         | R/W | 0x0 |

| 6     | clk_test_oe       | <b>内部时钟输出到 PA0</b><br>0x0: 关闭<br>0x1: 打开                                          | R/W | 0x0 |

| 5     | sys_err_resp_en   | <b>系统总线访问内存时，异常响应反馈使能</b><br>0x0: 关闭<br>0x1: 打开                                   | R/W | 0x0 |

| 4     | sys_err_int_en    | <b>系统总线访问出内存异常时，触发 NMI 中断</b><br>0x0: 关闭<br>0x1: 打开                               | R/W | 0x0 |

| 3     | hosc_loss_nmi_en  | <b>监控 XOSC 丢失触发 NMI 中断</b><br>0x0: 关闭<br>0x1: 打开                                  | R/W | 0x0 |

| 2     | rxev_enable       | <b>启用 PA1 作为 CPU 的接收事件</b><br>0x0: 关闭<br>0x1: 打开                                  | R/W | 0x0 |

| 1     | nmi_int_enable    | <b>开启 PA0 作为 CPU 的外部 NMI 输入</b><br>0x0: 关闭<br>0x1: 打开                             | R/W | 0x0 |

| 0     | lockup_enable     | <b>使能系统锁定触发系统复位</b><br>0x0: 关闭<br>0x1: 打开                                         | R/W | 0x0 |

#### 6.4.3.4. SYS\_CON2

| Bit(s) | Name      | Description                               | R/W | Reset |

|--------|-----------|-------------------------------------------|-----|-------|

| 31:30  | Reserved  | -                                         | -   | -     |

| 29:27  | pe_deb_en | GPIOE debounce 使能<br>对应控制 GPIOE0 ~GPIOE2  | R/W | 0x0   |

| 26:16  | pb_deb_en | GPIOB debounce 使能<br>对应控制 GPIOB0 ~GPIOB10 | R/W | 0x0   |

| 15:0   | pa_deb_en | GPIOA debounce 使能<br>对应控制 GPIOA0 ~GPIOA15 | R/W | 0x0   |

#### 6.4.3.5. SYS\_CON3

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31:0   | Reserved | -           | -   | -     |

#### 6.4.3.6. SYS\_CON4

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31:0   | Reserved | -           | -   | -     |

#### 6.4.3.7. SYS\_CON5

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31:0   | Reserved | -           | -   | -     |

#### 6.4.3.8. SYS\_CON6

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31:0   | Reserved | -           | -   | -     |

#### 6.4.3.9. SYS\_CON7

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31:0   | Reserved | -           | -   | -     |

#### 6.4.3.10. CLK\_CON0

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31:18  | Reserved | -           | R/W | -     |

|       |                 |                                                                                                                |     |     |

|-------|-----------------|----------------------------------------------------------------------------------------------------------------|-----|-----|

| 17:16 | lvd_debclk_sel  | <b>Lvd debounce 时钟选择</b><br>0x0: apb0_clk<br>0x1: HIRC 26M<br>0x2: LIRC 128K<br>0x3: LIRC 128K                 | R/W | 0x0 |

| 15:14 | comp_clk_sel    | <b>比较器时钟选择</b><br>0x0: LIRC 128K<br>0x1: divider output from HIRC 26M<br>0x2: sys_clk<br>0x3: XOSC             | R/W | 0x0 |

| 13:12 | Reserved        | -                                                                                                              | R/W | -   |

| 11:10 | gpioe_dbs_sel   | <b>GPIOE debounce 时钟选择</b><br>0x0: divider output from HIRC 26M<br>0x1: XOSC<br>0x2: sys_clk<br>0x3: LIRC 128K | R/W | 0x0 |

| 9:8   | gpiob_dbs_sel   | <b>GPIOB debounce 时钟选择</b><br>0x0: divider output from HIRC 26M<br>0x1: XOSC<br>0x2: sys_clk<br>0x3: LIRC 128K | R/W | 0x0 |

| 7:6   | gpioa_dbs_sel   | <b>GPIOA debounce 时钟选择</b><br>0x0: divider output from HIRC 26M<br>0x1: XOSC<br>0x2: sys_clk<br>0x3: LIRC 128K | R/W | 0x0 |

| 5     | Reserved        | -                                                                                                              | R/W | -   |

| 4     | pll_refclk_sel  | <b>P11 reference 时钟选择</b><br>0x0: HIRC 26M<br>1:XOSC                                                           | R/W | 0x0 |

| 3:2   | clock_to_io_sel | <b>Output clock 选择</b><br>0x0: sys_clk<br>0x1: HIRC 26M<br>0x2: LIRC 32K<br>0x3: XOSC                          | R/W | 0x0 |

| 1:0   | sysclk_sel      | <b>系统时钟选择</b><br>0x0: LIRC 128K<br>0x1: XOSC<br>0x2: HIRC 26M<br>0x3: pll_clk                                  | R/W | 0x0 |

#### 6.4.3.11. CLK\_CON1

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31     | Reserved | -           | -   | -     |

|       |               |                                                                                                                                                   |     |     |

|-------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|

| 30:28 | clk_to_io_div | <b>Clock to IO 分配比</b><br>0x0: divide by 1<br>0x1: divide by 2<br>0x2: divide by 3<br>...<br>0x6: divide by 7<br>0x7: close clock output          | R/W | 0x0 |

| 27:24 | hirc_clk_div  | <b>HIRC 26M clock 分频比</b><br>0x0: divide by 1<br>0x1: divide by 2<br>0x2: divide by 3<br>...<br>0xE: divide by 15<br>0xF: close HIRC divide clock | R/W | 0x0 |

| 23:19 | Reserved      | -                                                                                                                                                 | -   | -   |

| 18:16 | pll_clk_div   | <b>pll clock 分频比</b><br>when n=[1,6], pll_clk divide by n+1<br>when n=7, stoppll_clk<br>n=0 is forbidden                                          | R/W | 0x1 |

| 15:12 | apb1clk_div   | <b>PB1 clock 分频比</b><br>0x0: divide by 1<br>0x1: divide by 2<br>0x2: divide by 3<br>...<br>0xE: divide by 15<br>0xF: close apb1_clk               | R/W | 0x0 |

| 11:8  | apb0clk_div   | <b>APB0 clock 分频比</b><br>0x0: divide by 1<br>0x1: divide by 2<br>0x2: divide by 3<br>...<br>0xE: divide by 15<br>0xF: close apb0_clk              | R/W | 0x0 |

| 7:0   | sysclk_div    | <b>System clock 分频比</b><br>0x0: divide by 1<br>0x1: divide by 2<br>0x2: divide by 3<br>...<br>0xFE: divide by 255<br>0xFF: close sys_clk          | R/W | 0x0 |

#### 6.4.3.12. CLK\_CON2

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31     | reserved | -           | -   | -     |

|       |                   |                                                                      |     |     |

|-------|-------------------|----------------------------------------------------------------------|-----|-----|

| 30    | clk_source_en_bps | <b>p11_clk and xosc clock glitch free? ? ?</b><br>0x0: 打开<br>0x1: 关闭 | R/W | 0x1 |

| 29    | cp_clk_en         | <b>CP 模式使能 CPU 时钟</b><br>0x0: 关闭<br>0x1: 打开                          | R/W | 0x0 |

| 28    | test_clk_en       | <b>ATE 时钟输出使能</b><br>0x0: 关闭<br>0x1: 打开                              | R/W | 0x0 |

| 27    | comp_clk_en       | <b>比较器时钟使能</b><br>0x0: 关闭<br>0x1: 打开                                 | R/W | 0x1 |

| 26    | Reserved          | -                                                                    | -   | -   |

| 25    | crc_clk_en        | <b>CRC 时钟使能</b><br>0x0: 关闭<br>0x1: 打开                                | R/W | 0x1 |

| 24    | eflash_mem_clk_en | <b>eflash erase/program 时钟使能</b><br>0x0: 关闭<br>0x1: 打开               | R/W | 0x1 |

| 23    | Reserved          | -                                                                    | -   | -   |

| 22    | hwdiv_clk_en      | <b>硬件除法器时钟使能</b><br>0x0: 关闭<br>0x1: 打开                               | R/W | 0x0 |

| 21:19 | Reserved          | -                                                                    | -   | -   |

| 18    | uart1_clk_en      | <b>UART1 时钟使能</b><br>0x0: 关闭<br>0x1: 打开                              | R/W | 0x1 |

| 17    | uart0_clk_en      | <b>UART0 时钟使能</b><br>0x0: 关闭<br>0x1: 打开                              | R/W | 0x1 |

| 16    | spi1_clk_en       | <b>SPI1 时钟使能</b><br>0x0: 关闭<br>0x1: 打开                               | R/W | 0x1 |

| 15    | spi0_clk_en       | <b>SPI0 时钟使能</b><br>0x0: 关闭<br>0x1: 打开                               | R/W | 0x1 |

| 14    | epwm_clk_en       | <b>EPWM 时钟使能</b><br>0x0: 关闭<br>0x1: 打开                               | R/W | 0x1 |

| 13    | timer5_clk_en     | <b>TIMER5 时钟使能</b><br>0x0: 关闭<br>0x1: 打开                             | R/W | 0x1 |

| 12    | timer3_clk_en     | <b>TIMER3 时钟使能</b><br>0x0: 关闭<br>0x1: 打开                             | R/W | 0x1 |

|     |                |                                           |     |     |

|-----|----------------|-------------------------------------------|-----|-----|

| 11  | timer2_clk_en  | <b>TIMER2 时钟使能</b><br>0x0: 关闭<br>0x1: 打开  | R/W | 0x1 |

| 10  | timer1_clk_en  | <b>TIMER1 时钟使能</b><br>0x0: 关闭<br>0x1: 打开  | R/W | 0x1 |

| 9   | timer0_clk_en  | <b>TIMERO 时钟使能</b><br>0x0: 关闭<br>0x1: 打开  | R/W | 0x1 |

| 8   | wdt_clk_en     | <b>WDT 时钟使能</b><br>0x0: 关闭<br>0x1: 打开     | R/W | 0x1 |

| 7   | wdt_sys_clk_en | <b>WDT sys 时钟使能</b><br>0x0: 关闭<br>0x1: 打开 | R/W | 0x1 |

| 6   | timer4_clk_en  | <b>TIMER4 时钟使能</b><br>0x0: 关闭<br>0x1: 打开  | R/W | 0x1 |

| 5:3 | Reserved       | -                                         | -   | -   |

| 2   | sram0_clk_en   | <b>SRAM0 时钟使能</b><br>0x0: 关闭<br>0x1: 打开   | R/W | 0x1 |

| 1   | ahb1_clk_en    | <b>AHB1 时钟使能</b><br>0x0: 关闭<br>0x1: 打开    | R/W | 0x1 |

| 0   | ahb0_clk_en    | <b>AHB0 时钟使能</b><br>0x0: 关闭<br>0x1: 打开    | R/W | 0x1 |

#### 6.4.3.13. CLK\_CON3

| Bit(s) | Name           | Description                                           | R/W | Reset |

|--------|----------------|-------------------------------------------------------|-----|-------|

| 31     | hrcosc_en_flag | <b>HIRC 26M 工作状态</b><br>0x0: not ready<br>0x1: ready  | RO  | 0x1   |

| 30:29  | Reserved       | -                                                     | -   | -     |

| 28     | hrcosc_vtest2  | <b>VDD 测试使能</b><br>输出 VTSOUT<br>0x0: 关闭<br>0x1: 打开    | R/W | 0x0   |

| 27     | hrcosc_vtest1  | <b>VDDOSC 测试使能</b><br>输出 VTSOUT<br>0x0: 关闭<br>0x1: 打开 | R/W | 0x0   |

| 26     | hrcosc_vsel    | <b>LDO 参考选择</b>                                       | R/W | 0x0   |

|       |             |                                                           |     |      |

|-------|-------------|-----------------------------------------------------------|-----|------|

|       |             | 0x0: Voltage bias<br>0x1: Current                         |     |      |

| 25:19 | hrcosc_sc   | <b>HRCOSC 频率控制</b><br>0x0: lowest<br>...<br>0x7F: highest | R/W | 0x0  |

| 18    | hrcosc_ldos | <b>RCOSC LDO 电压选择</b><br>0x0: 1.5v<br>0x1: 1.6v           | R/W | 0x0  |

| 17    | hrcosc_en   | <b>RCOSC 使能</b><br>0x0: disable<br>0x1: enable            | R/W | 0x1  |

| 16:15 | hxosc_fbres |                                                           | R/W | 0x3  |

| 14:10 | hxosc_dr    |                                                           | R/W | 0x10 |

| 9:6   | hxosc_cto   |                                                           | R/W | 0x0  |

| 5:2   | hxosc_cti   |                                                           | R/W | 0x0  |

| 1     | hxosc_hy    |                                                           | R/W | 0x1  |

| 0     | hxosc_en    | <b>XOSC 使能</b><br>0x0: 关闭<br>0x1: 打开                      | R/W | 0x0  |

#### 6.4.3.14. CLK\_CON4

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31:0   | Reserved | -           | -   | -     |

#### 6.4.3.15. CLK\_CON5

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31:0   | Reserved | -           | -   | -     |

#### 6.4.3.16. CLK\_CON6

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31:0   | Reserved | -           | -   | -     |

#### 6.4.3.17. CLK\_CON7

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31:0   | Reserved | -           | -   | -     |

#### 6.4.3.18. HOSC\_MNT

| Bit(s) | Name              | Description                                                                       | R/W | Reset  |

|--------|-------------------|-----------------------------------------------------------------------------------|-----|--------|

| 31:16  | high_limit        | XOSC 工作上限限制                                                                       | R/W | 0x1450 |

| 15     | hosc_mnt_en       | XOSC 监控功能使能<br>0x0: 关闭<br>0x1: 打开                                                 | R/W | 0x0    |

| 14     | hosc_loss_pending | 读取寄存器<br>0x0: 正常状态<br>0x1: 挂起, 表示外部 xosc 失败<br>写寄存器<br>0x0: 清除 pending<br>0x1: 无效 | R/W | 0x0    |

| 13     | hosc_loss_sw_en   | 当检测到外部 osc 故障时, 硬件自动将 osc 时钟从 xosc 切换到 HIRC<br>0x0: 关闭<br>0x1: 打开                 | R/W | 0x0    |

| 12:0   | low_limit         | XOSC 工作下限限制                                                                       | R/W | 0xA7   |

#### 6.4.3.19. SYS\_ERR

| Bit(s) | Name     | Description                                         | R/W | Reset |

|--------|----------|-----------------------------------------------------|-----|-------|

| 31:1   | Reserved | -                                                   | -   | -     |

| 1      | clk_err  | 时钟异常标志<br>0x0: 工作正常<br>0x1: 时钟使用错误时, 此位可由硬件设置, 软件清除 | R/W | 0     |

| 0      | sys_err0 | 系统访问异常<br>如果设置 sys_err_int_en, 这个挂起会导致 NMI 中断       | R/W | 0     |

| clk_err 触发情况                     |              |              |              |

|----------------------------------|--------------|--------------|--------------|

|                                  | lirc disable | hirc disable | xosc disable |

| sys_clk_sel_lirc                 | √            |              |              |

| sys_clk_sel_hirc                 |              | √            |              |

| sys_clk_sel_xosc                 |              |              | √            |

| sys_clk_sel_pll&pll_ref_sel_lirc |              |              |              |

| sys_clk_sel_pll&pll_ref_sel_hirc |              | √            |              |

| sys_clk_sel_pll&pll_ref_sel_xosc |              |              | √            |

#### 6.4.3.20. WKUP\_CON

| Bit(s) | Name      | Description                                                                                    | R/W | Reset |

|--------|-----------|------------------------------------------------------------------------------------------------|-----|-------|

| 31:1   | Reserved  | -                                                                                              | -   | -     |

| 29:24  | wkup_pnd  | <b>Wakeup IO 的边沿检测触发</b><br>0x0: 无触发<br>0x1: 已触发<br>对应关系:<br>BIT24->port0、BIT25->port1 以此类推    | RO  | -     |

| 23:22  | Reserved  | -                                                                                              | -   | -     |

| 21:16  | clr_pnd   | <b>Wakeup pending 清除</b><br>写 1 清除                                                             | WO  | -     |

| 15:14  | Reserved  | -                                                                                              | -   | -     |

| 13:8   | wkup_edge | <b>Wakeup 的边沿唤醒选择</b><br>0x0: 上升沿触发<br>0x1: 下降沿触发                                              | R/W | 0x0   |

| 7:6    | Reserved  | -                                                                                              | -   | -     |

| 5:0    | wkup_en   | <b>Wakeup 使能</b><br>0x0: 关闭<br>0x1: 打开<br>BIT0~BIT3: 外部 GPIO 唤醒<br>BIT4: 比较器唤醒<br>BIT5: LVD 唤醒 | R/W | 0x0   |

#### 6.4.3.21. LP\_CON

| Bit(s) | Name             | Description                                                | R/W | Reset |

|--------|------------------|------------------------------------------------------------|-----|-------|

| 31:9   | Reserved         | -                                                          | -   | -     |

| 8      | lp_mode          | <b>LP 使能</b><br>0x0: 关闭<br>0x1: 打开                         | 0x0 | R/W   |

| 7      | lp_mode_auto_en  | <b>Sleep 模式下自动使能 LP 模式</b><br>0x0: 关闭<br>0x1: 打开           | 0x0 | R/W   |

| 6      | hirc_auto_enable | <b>XOSC 检测出现异常时, 自动使能并切换 HIRC26M</b><br>0x0: 关闭<br>0x1: 打开 | 0x0 | R/W   |

| 5      | rc32k_soft_en    | <b>LIRC 使能</b><br>0x0: 关闭<br>0x1: 打开                       | 0x1 | R/W   |

| 4      | rc32k_auto_dis   | <b>进入 sleep 模式自动关闭 LIRC</b><br>0x0: 关闭<br>0x1: 打开          | 0x0 | R/W   |

| 3      | hirc_auto_dis    | <b>进入 sleep/stop 模式自动关闭 LIRC</b><br>0x0: 关闭                | 0x0 | R/W   |

|   |                |                                                 |     |     |

|---|----------------|-------------------------------------------------|-----|-----|

|   |                | 0x1: 打开                                         |     |     |

| 2 | sram0_auto_dis | 进入 sleep/stop 模式自动关闭 SRAM<br>0x0: 关闭<br>0x1: 打开 | 0x0 | R/W |

| 1 | stopclk        | 进入 stop 模式<br>0x0: 关闭<br>0x1: 打开                | 0x0 | R/W |

| 0 | sleep          | 进入 sleep 模式<br>0x0: 关闭<br>0x1: 打开               | 0x0 | R/W |

#### 6.4.3.22. MBIST\_CON

| Bit(s) | Name              | Description                                                         | R/W | Reset |

|--------|-------------------|---------------------------------------------------------------------|-----|-------|

| 31:21  | Reserved          | -                                                                   | -   | -     |

| 20     | mbist_fail_h      | <b>MBIST 异常标志</b><br>读操作:<br>0x1: MBIST 异常<br>写操作:<br>0x1: 清除异常标志   | R/W | 0x0   |

| 19     | mbist_tst_done    | <b>MBIST 完成标志</b><br>读操作:<br>0x1: MBIST 测试完成<br>写操作:<br>0x1: 清除完成标志 | R/W | 0x0   |

| 18     | mbist_clk_en      | <b>MBIST 时钟使能</b><br>0x0: 关闭<br>0x1: 打开                             | R/W | 0x0   |

| 17:12  | Reserved          | -                                                                   | -   | -     |

| 11     | mbist_rf1p_debugz | <b>MBIST rf1p 调试使能</b><br>0x0: 关闭<br>0x1: 打开                        | R/W | 0x0   |

| 10     | mbist_rf1p_hold_l | <b>MBIST rf1p 调试使能</b><br>0x0: 关闭<br>0x1: 打开                        | R/W | 0x0   |

| 9      | mbist_rf1p_test_h | <b>MBIST rf1p 调试使能</b><br>0x0: 关闭<br>0x1: 打开                        | R/W | 0x0   |

| 8:0    | Reserved          | -                                                                   | -   | -     |

#### 6.4.3.23. MBIST\_MISR

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31:0   | Reserved | -           | -   | -     |

#### 6.4.3.24. MODE

| Bit(s) | Name     | Description | R/W | Reset |

|--------|----------|-------------|-----|-------|

| 31:0   | Reserved | -           | -   | -     |

#### 6.4.3.25. PMU\_CON

| Bit(s) | Name     | Description                                                                                                                                                                                                                                           | R/W | Reset |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 31:23  | Reserved | -                                                                                                                                                                                                                                                     | -   | -     |

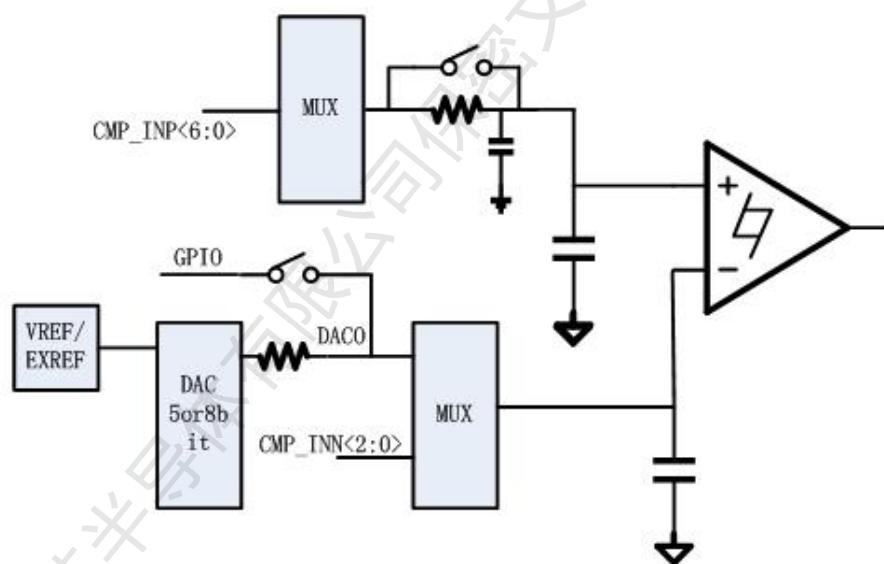

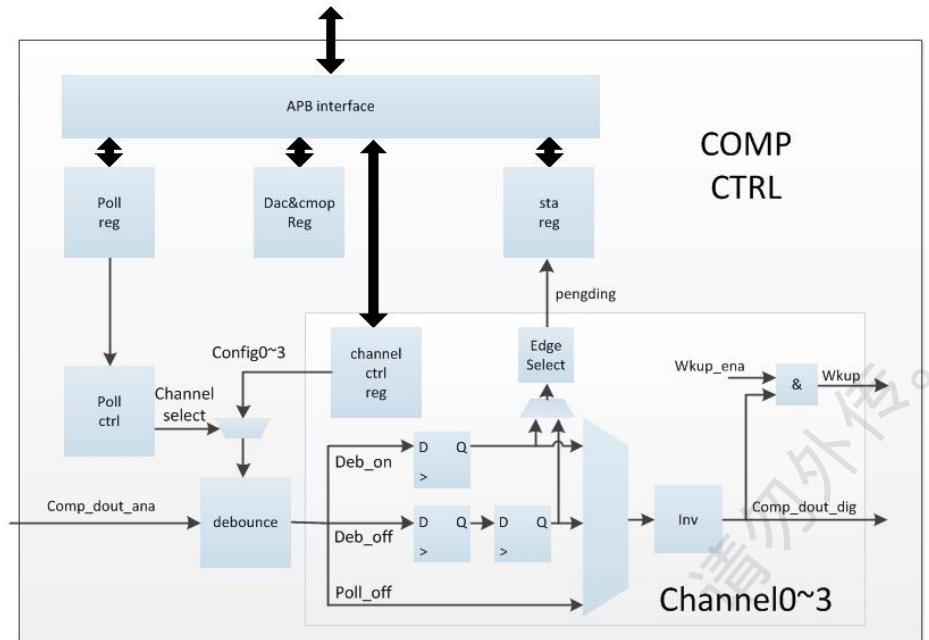

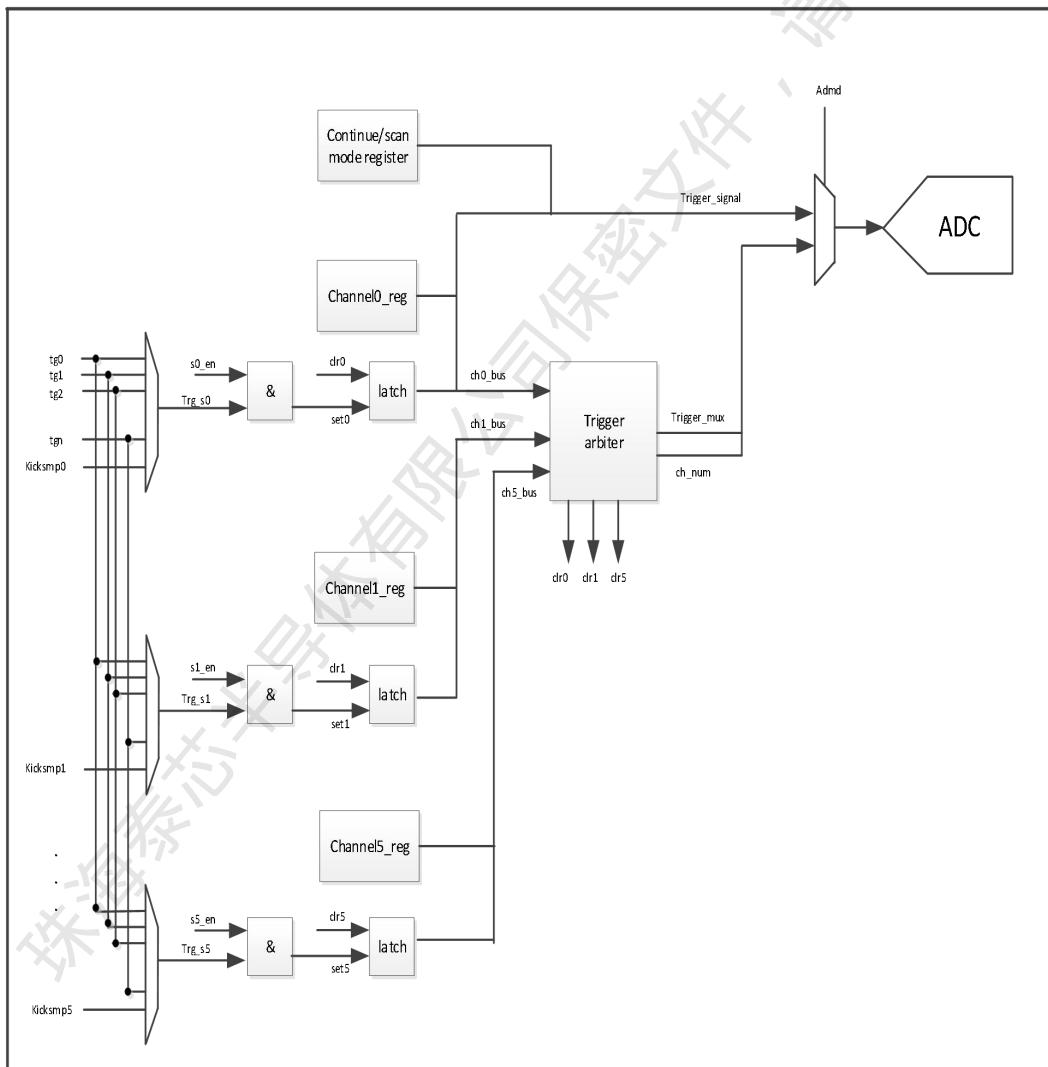

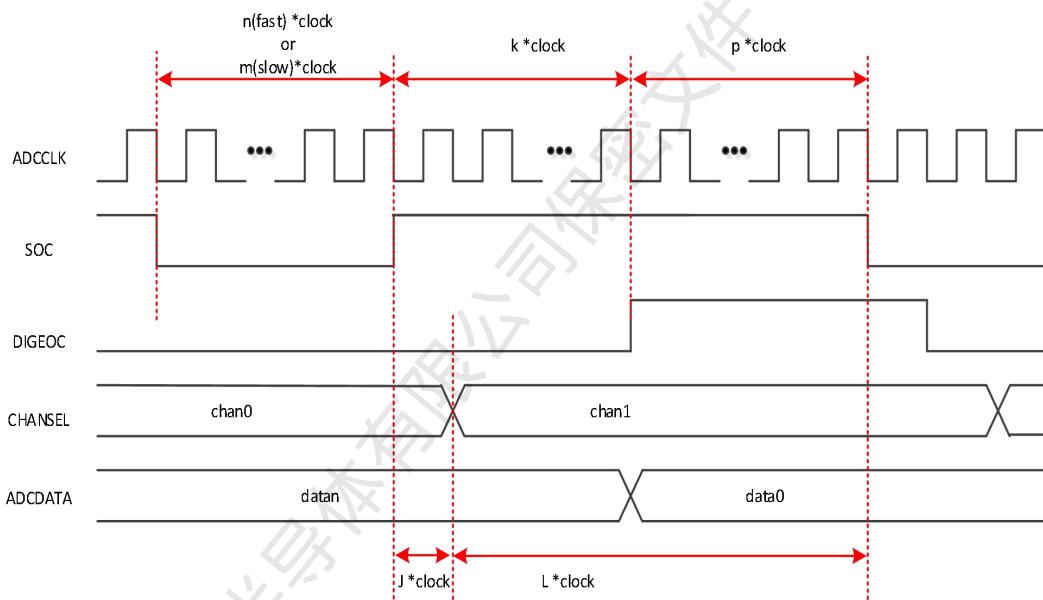

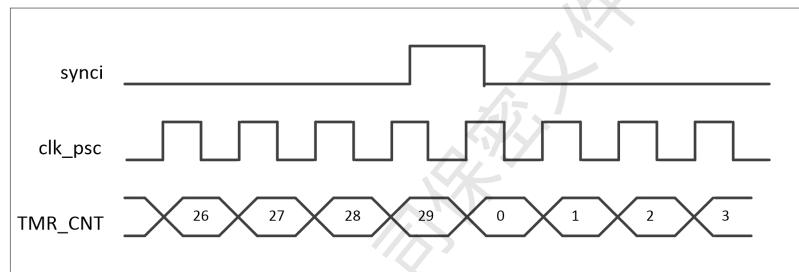

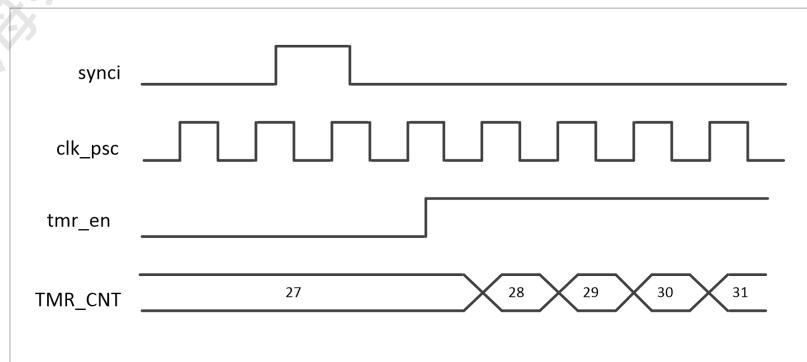

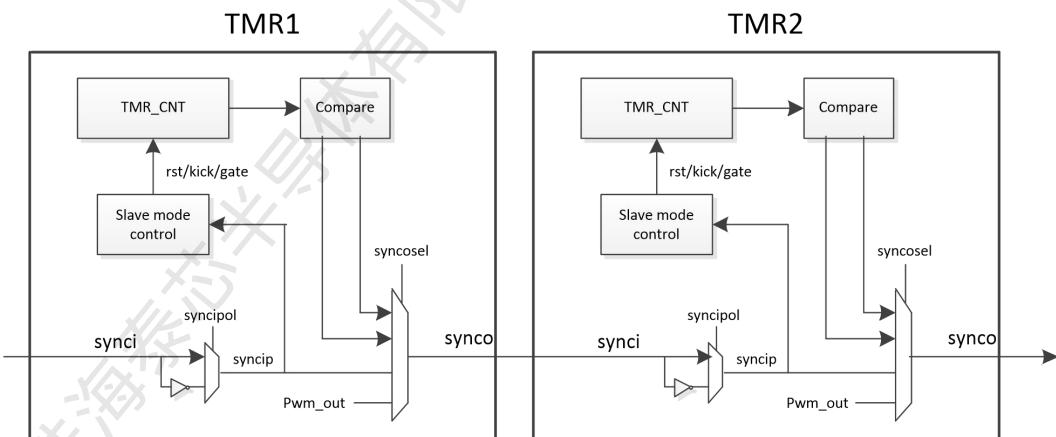

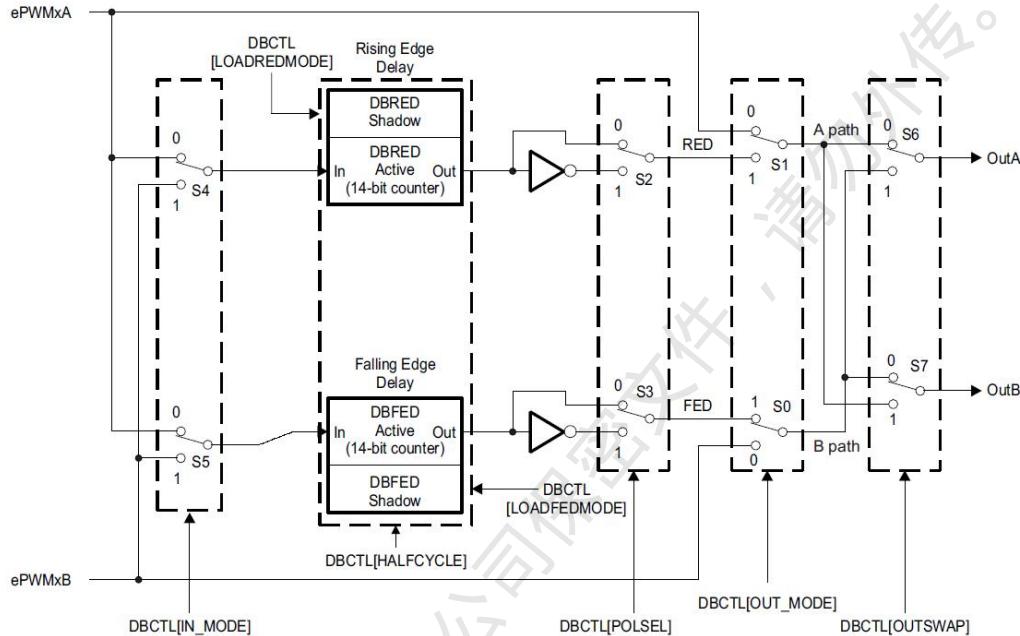

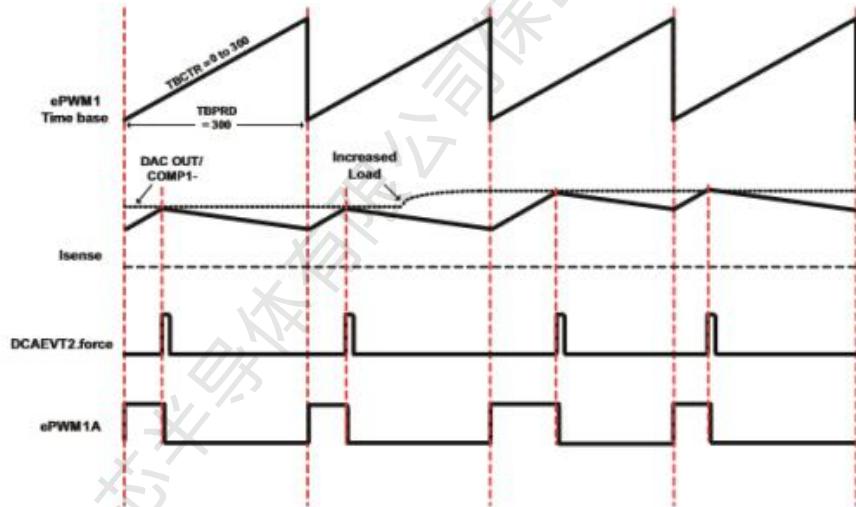

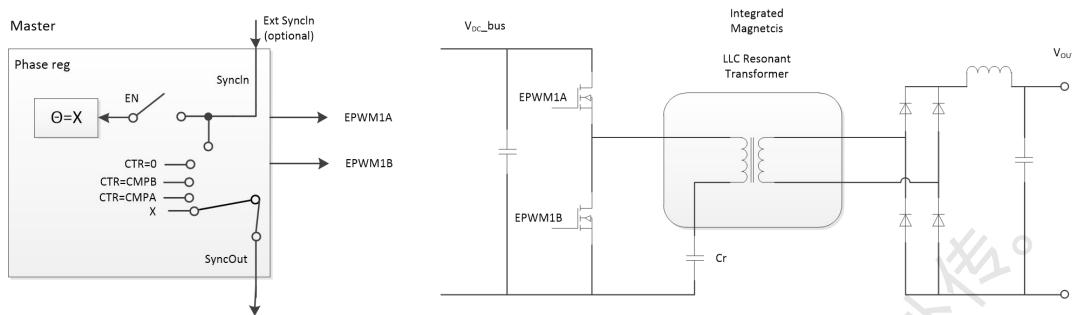

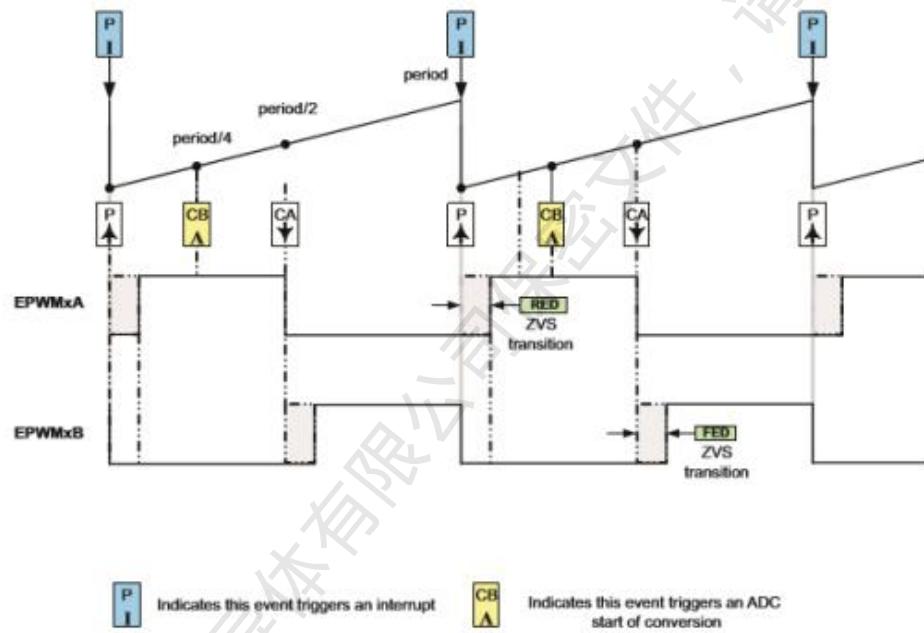

| 22:20  | dset     | -                                                                                                                                                                                                                                                     | R/W | 0x4   |